Freescale Semiconductor MPC8260 User Manual

Page 1317

Reference Manual (Rev 1) Errata

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

B-15

and transmitted a byte at a time with lsb first:

first

r_stuv_ghij_klmn

last

39.4.3, 39-8

In Table 39-3, the description of DIV should read as follows (changes appear in

boldface):

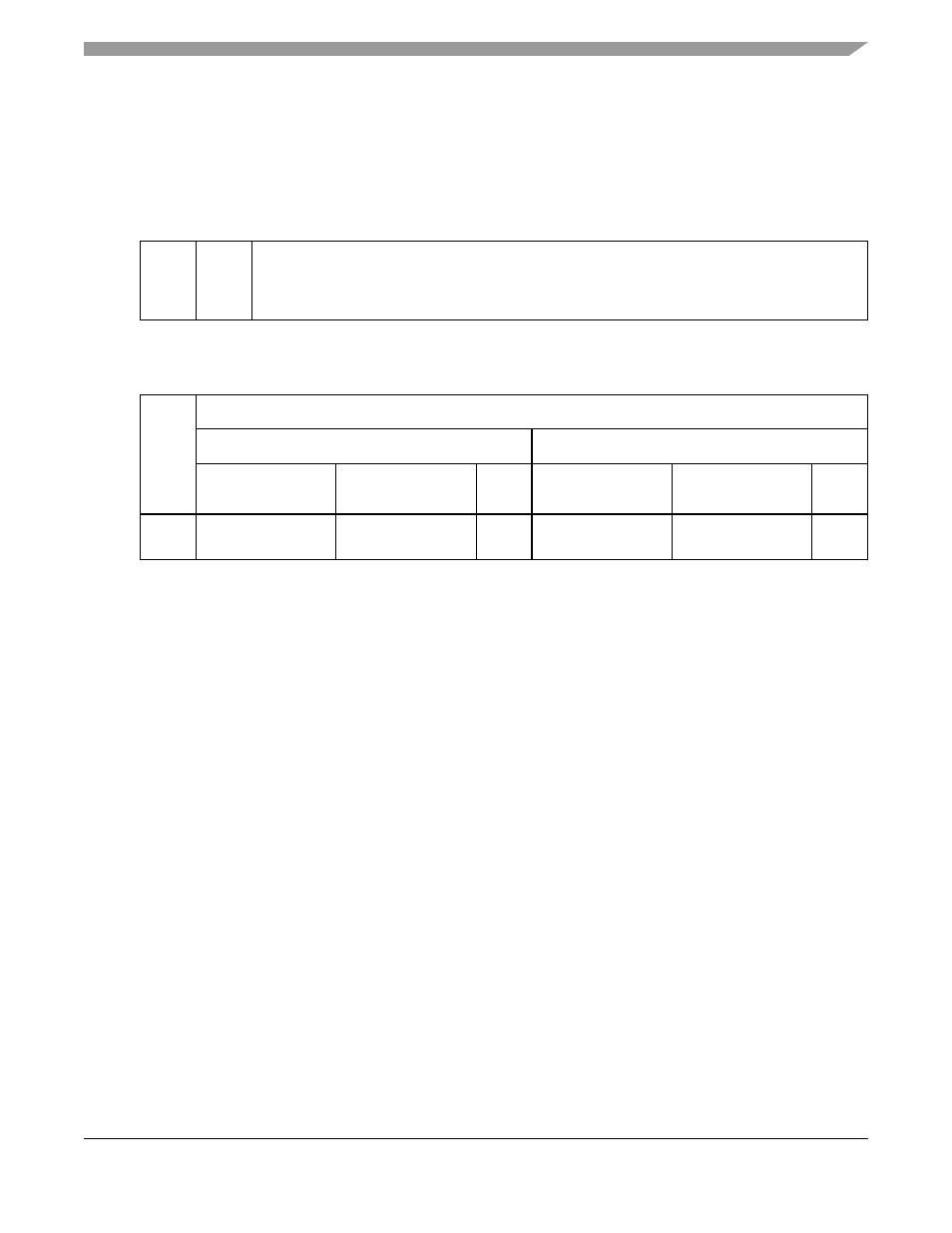

40-5, 40-10

In Table 40-5, add TDM_A1:L1TXD to PA9 in the column for PSORA = 1 and

PDIRA = 0, as shown below:

40-5, 40-16

In Table 40-7, the note attached to SPI: SPISEL at PC1 is incorrect. It should refer

to note 2 (“available only when the primary option for this function is not used”)

and not note 3.

0–7

DIV

Division ratio 0–7. Specifies the divide ratio of the BRG divider in the I

2

C clock generator. The output

of the prescaler is divided by 2 * ([DIV0–DIV7] + 3 + (2 * I2MOD[FLT])) and the clock has a 50% duty

cycle. DIV must be programmed to a minimum value of 3 if the digital filter is disabled

(I2MOD[FLT] = 0) and 6 if it is enabled (I2MOD[FLT] = 1).

Pin

Pin Function

PSORA = 0

PSORA = 1

PDIRA = 1 (Output)

PDIRA = 0 (Input)

Default

Input

PDIRA = 1 (Output)

PDIRA = 0 (Input, or

In/out if Specified)

Default

Input

PA9

SMC2: SMTXD

TDM_A1: L1TXD[0]

Output, nibble

TDM_A1: L1TXD

Inout, serial

GND