Table 9-56. ophpr field descriptions, Ophpr field descriptions -76 – Freescale Semiconductor MPC8260 User Manual

Page 382

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-76

Freescale Semiconductor

An external PCI master reads the outbound queue port register. This causes the PCI bridge’s I

2

O unit to

read the MFA from local memory pointed to by the OPTPR+QBAR. The unit then advances the OPTPR.

When the FIFO is empty (head and tail pointers are equal), the unit returns 0xFFFF_FFFF.

The local processor posts MFAs to the outbound post list FIFO that is pointed to by the outbound

post_FIFO head pointer register, described in

. The local processor is

responsible for updating this register.

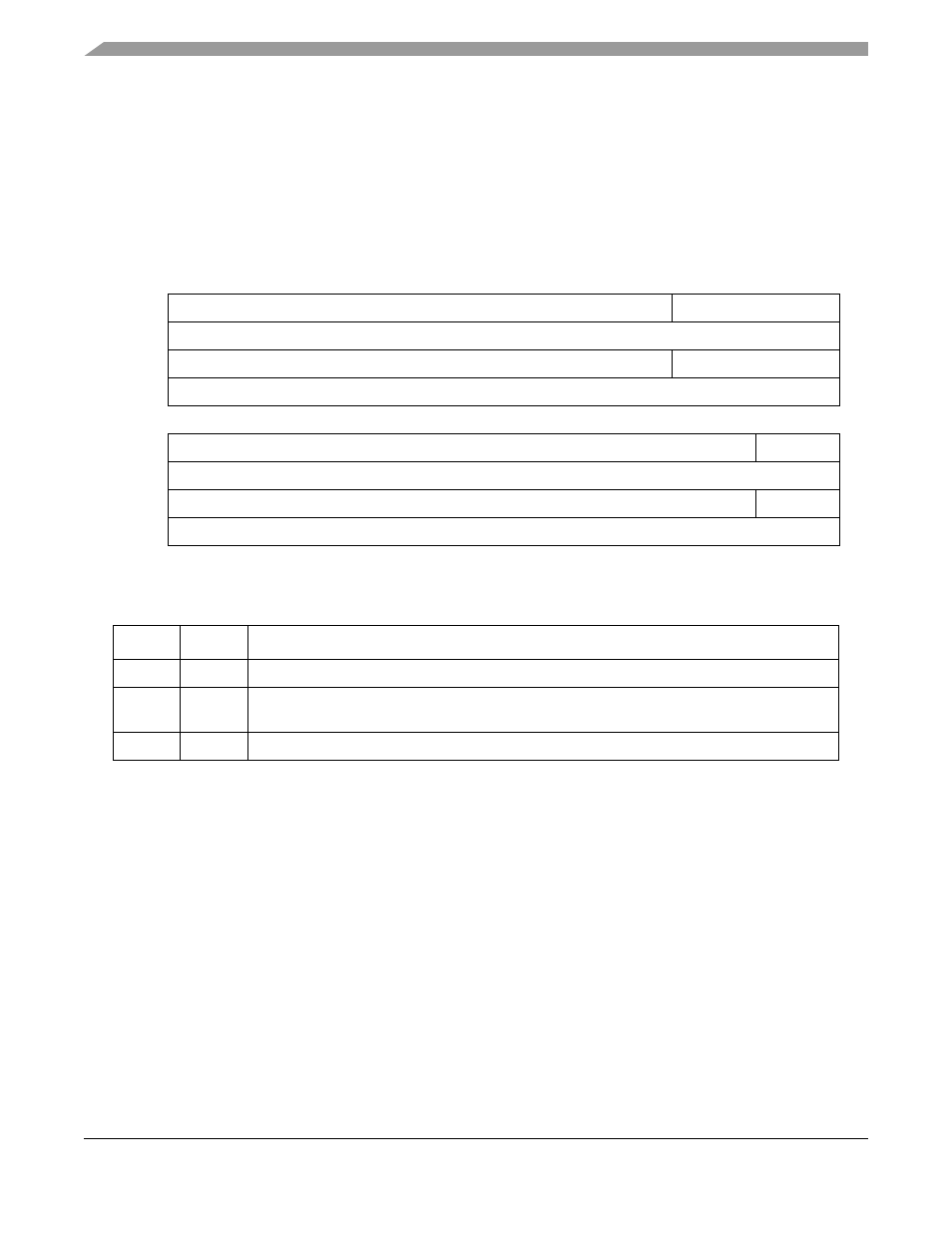

Figure 9-71. Outbound Post_FIFO Head Pointer Register (OPHPR)

Posted MFAs are picked up by PCI hosts that are pointed to by the outbound post_FIFO tail pointer

register, described in

. The PCI read is performed at the outbound queue port.

Hardware automatically advances this register after every read.

31

20

19

16

Field

QBA

OPHP

Reset

0000_0000_0000_0000

R/W

R

R/W

Addr

0x104D2

15

2

1

0

Field

OPHP

—

Reset

0000_0000_0000_0000

R/W

R/W

R

Addr

0x104D0

Table 9-56. OPHPR Field Descriptions

Bits

Name

Description

31–20

QBA

Queue base address. When read returns the contents of QBAR bits 31-20.

19–2

OPHP

Outbound post_FIFO head pointer. Local memory offset of the head pointer of the outbound

post list FIFO.

1–0

—

Reserved, should be cleared.