Table 9-50. ifhpr field descriptions, Ifhpr field descriptions -71 – Freescale Semiconductor MPC8260 User Manual

Page 377

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-71

The following registers should be accessed only from the 60x bus and only in agent mode. Accesses while

in host mode or from the PCI bus have undefined results.

9.12.3.2.1

Inbound Free_FIFO Head Pointer Register (IFHPR) and

Inbound Free_FIFO Tail Pointer Register (IFTPR)

The inbound free list FIFO holds the list of empty inbound MFAs. The external PCI master reads IFQPR

(refer to

Section 9.12.3.4.1, “Inbound FIFO Queue Port Register (IFQPR)”

) which returns the MFA

pointed to by the inbound free list tail pointer register, (IFTPR+QBAR). The PCI bridge’s I

2

O unit then

advances IFTPR.

If the inbound free list is empty (no free MFA entries), the unit returns 0xFFFF_FFFF.

Free MFAs from the local processor are posted to the inbound free list FIFO that is pointed to by the

inbound free_FIFO head pointer register, described in

. The local processor is

responsible for updating this register.

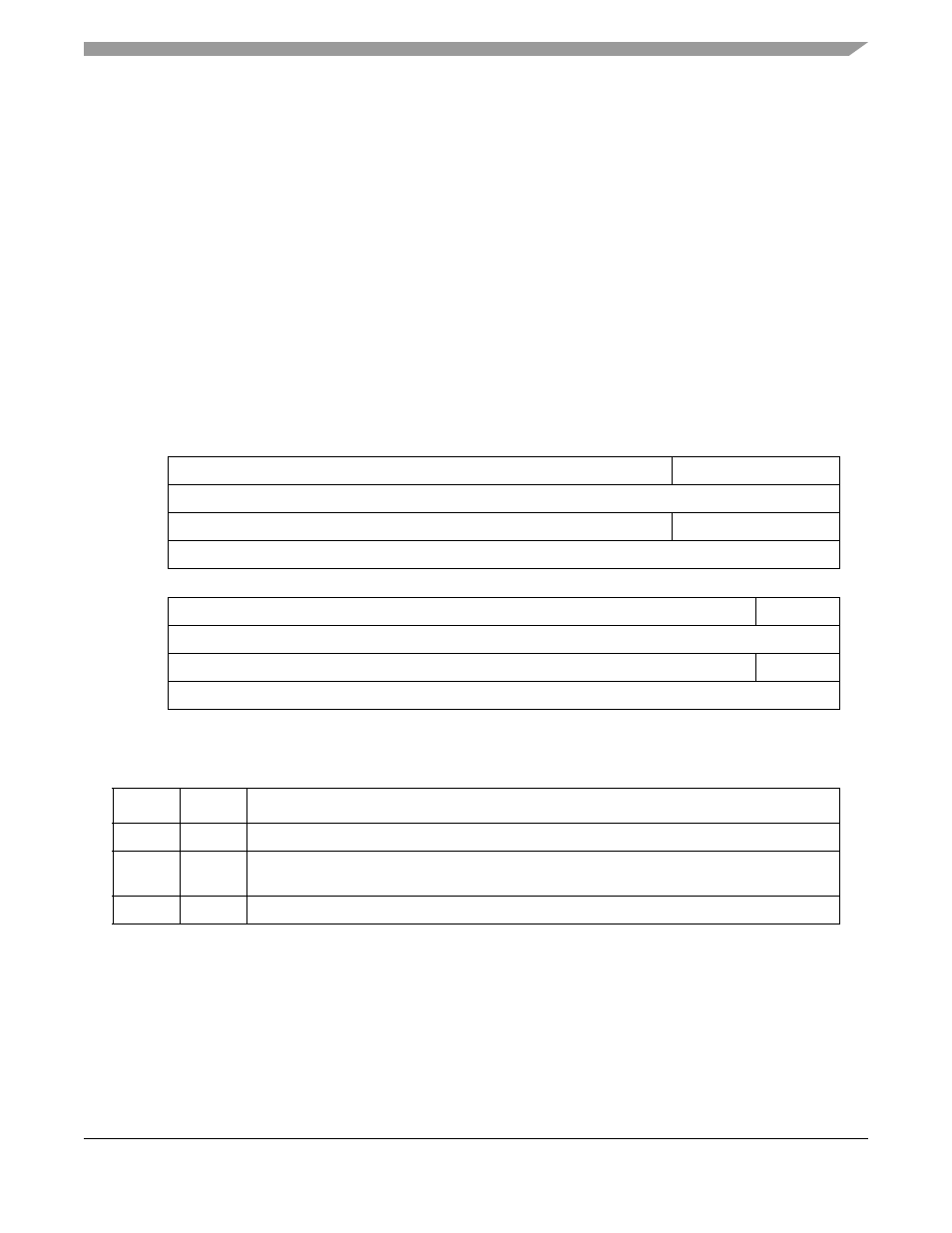

Figure 9-65. Inbound Free_FIFO Head Pointer Register (IFHPR)

Free MFAs are picked up by the PCI masters that are pointed to by the inbound free_FIFO tail pointer,

described in

. The PCI read is performed at the inbound queue port. Hardware

automatically advances this register after every read.

31

20

19

16

Field

QBA

IFHP

Reset

0000_0000_0000_0000

R/W

R

R/W

Addr

0x104A2

15

2

1

0

Field

IFHP

—

Reset

0000_0000_0000_0000

R/W

R/W

R

Addr

0x104A0

Table 9-50. IFHPR Field Descriptions

Bits

Name

Description

31–20

QBA

Queue base address. When read returns the contents of QBAR bits 31-20.

19–2

IFHP

Inbound free_fifo head pointer. Local memory offset of the head pointer of the inbound free list

FIFO.

1–0

—

Reserved, should be cleared.