Table 34-6. tcgsr field descriptions, 3 tc layer cell counters, 1 received cell counter [1-8] (tc_rccx) – Freescale Semiconductor MPC8260 User Manual

Page 1190: 2 transmitted cell counter [1-8] (tc_tccx), 3 errored cell counter [1-8] (tc_eccx), 4 corrected cell counter [1-8] (tc_cccx), 5 transmitted idle cell counter [1-8] (tc_iccx), Tc layer cell counters -12, Received cell counter [1–8] (tc_rccx) -12, Transmitted cell counter [1–8] (tc_tccx) -12

ATM Transmission Convergence Layer

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

34-12

Freescale Semiconductor

describes TCGSR fields.

f

34.4.3

TC Layer Cell Counters

Each TC block maintains six memory-mapped 16-bit performance cell counters that are updated during

operation and can be read by the host. If a counter overflows, it wraps back to zero and generates a

maskable interrupt. These counters are automatically cleared when read if TCMODE[CM] = 0; see

Section 34.4.1.1, “TC Layer Mode Register [1–8] (TCMODEx).”

34.4.3.1

Received Cell Counter [1–8] (TC_RCC

x)

This cell counter is updated whenever a received cell without HEC errors is passed to the Rx UTOPIA

FIFO.

34.4.3.2

Transmitted Cell Counter [1–8] (TC_TCC

x)

This cell counter is updated whenever the transmission of a cell is completed.

34.4.3.3

Errored Cell Counter [1–8] (TC_ECC

x)

This cell counter is updated whenever a received errored cell (cell with header error) is discarded.

34.4.3.4

Corrected Cell Counter [1–8] (TC_CCC

x)

This cell counter is updated whenever a received cell with a HEC single bit error is corrected. If header

single bit error correction is not enabled (TCMODE[SBC] is set), this counter is not updated. (All errored

cells are counted by the errored cell counter (ECC).)

34.4.3.5

Transmitted IDLE Cell Counter [1–8] (TC_ICC

x)

This cell counter is updated whenever an idle cell is transmitted.

0

1

2

3

4

5

6

7

8

15

Field CD1

CD2

CD3

CD4

CD5

CD6

CD7

CD8

—

Reset

0000_0000_0000_0000

R/W

R

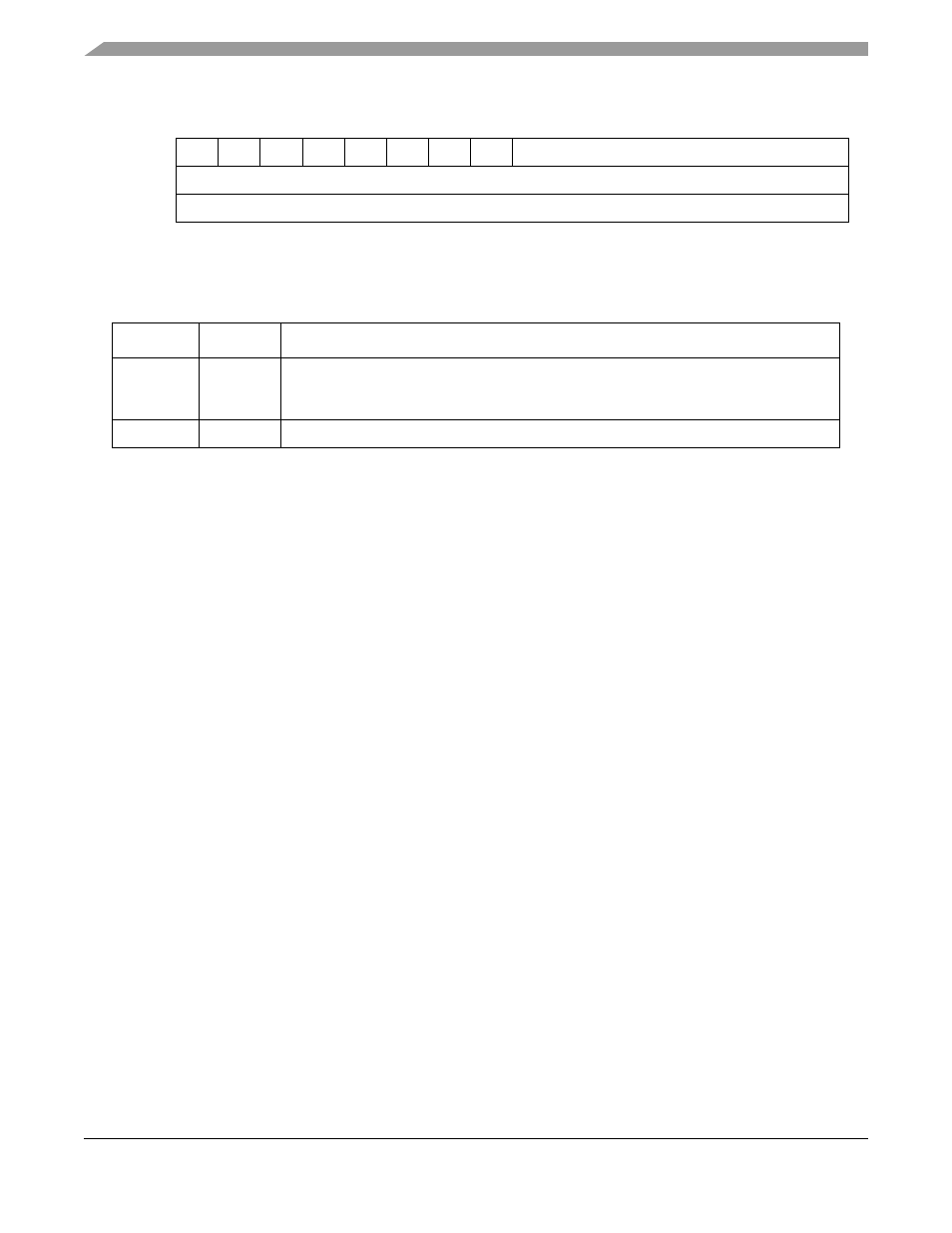

Figure 34-9. TC Layer General Status Register (TCGSR)

Table 34-6. TCGSR Field Descriptions

Bits

Name

Description

0–7

CDx

Cell Delineation. The cell delineation state machine status of TCx.

0 Cell delineation state machine is in Hunt or Pre-Synch modes.

1 Cell delineation machine is in Synch mode.

8–15

—

Reserved