16 external aal1 ces statistics tables, Table 31-15. aal1 ces external statistics table, 17 ces-specific additions to the mcc – Freescale Semiconductor MPC8260 User Manual

Page 1060: 18 application considerations, External aal1 ces statistics tables -44, Ces-specific additions to the mcc -44, Application considerations -44, Aal1 ces external statistics table -44

ATM AAL1 Circuit Emulation Service

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

31-44

Freescale Semiconductor

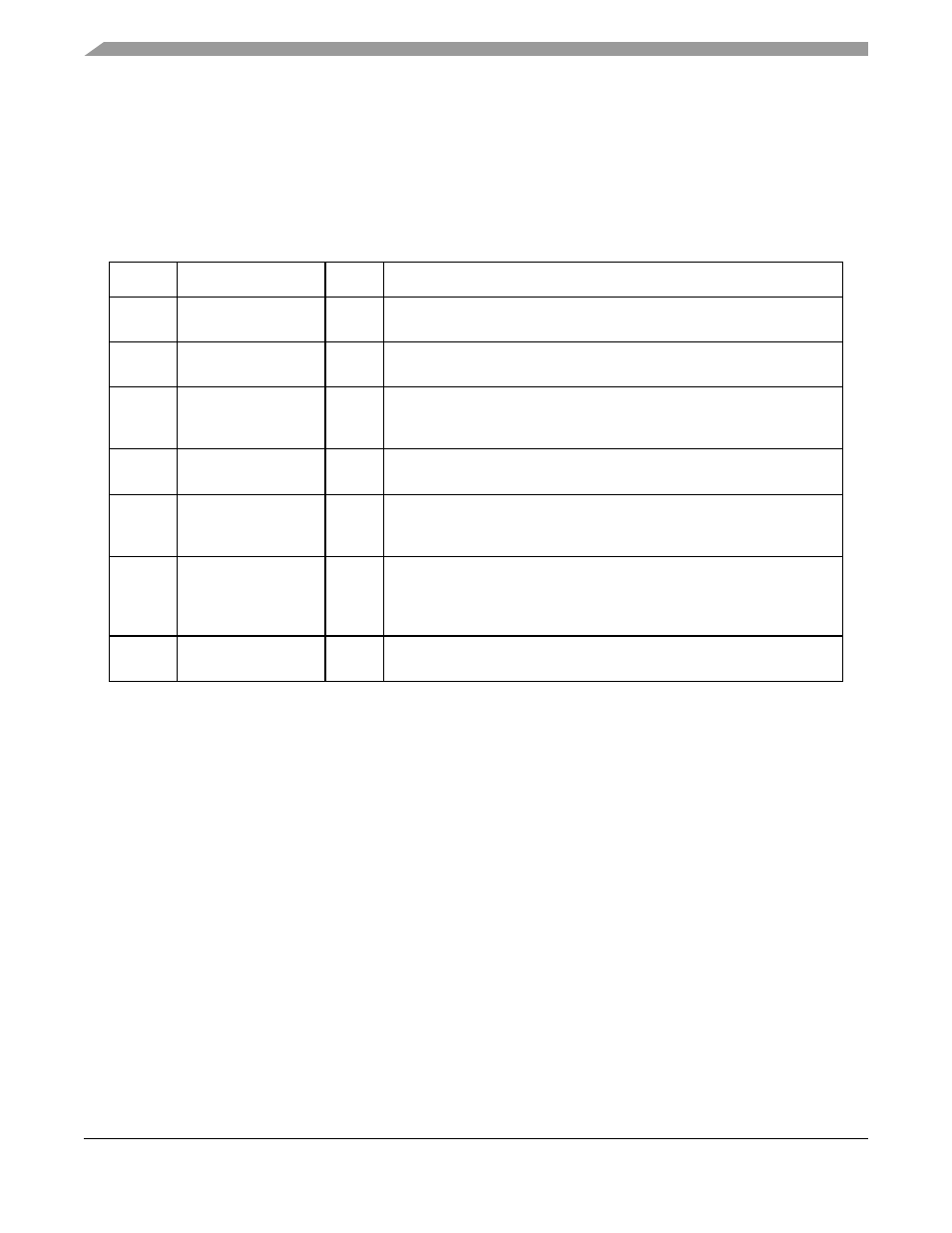

31.16 External AAL1 CES Statistics Tables

An AAL1 CES statistics table, shown in

, resides in the external memory and holds AAL1 CES

statistics on a per-VC basis. AAL1_Ext_STATT_BASE points to the base address of these tables. Each

AAL1 channel has its own table with a starting address given by AAL1_Ext_STATT_BASE +

ATM_CHANNEL#

× 16.

Note that both the internal and the external statistics tables should be cleared by the user.

31.17 CES-Specific Additions to the MCC

Additions to the MCC global parameter RAM and modifications to the channel-specific CHAMR and

INTMASK registers have been implemented to support CES operation. Refer to

Parameters for AAL1 CES Usage,”

Section 28.3.3.1.1, “Interrupt Circular Table Entry and Interrupt Mask

Section 28.3.1.3, “Channel Mode Register (CHAMR)—HDLC Mode,”

for more information.

31.18 Application Considerations

•

The buffer size (MCC [MRBLR]) must be a multiple of 8 octets.

•

The CAS buffer operates in continuous mode with newer signaling information continuously

overwriting older signaling.

•

The CES application does not use super-frame synchronization for the data flow in ATM-to-TDM

and TDM-to-ATM interworking. However, for the signaling flow, the PowerQUICC II uses the

super-frame sync signal to know when to supply the signaling information to the external framer.

Table 31-15. AAL1 CES External Statistics Table

Offset Name

Width

Description

0x00

Rx_AAL1_LOST

Hword

16-bit cyclic counter. Counts the number of AAL1 lost cells events. See

Section 31.6, “3-Step-SN Algorithm

.”

0x02

Rx_AAL1_MISS

Hword

16-bit cyclic counter. Counts the number of AAL1 misinserted events. See

Section 31.6, “3-Step-SN Algorithm

.”

0x04

Rx_AAL1_SCE

Hword

16-bit cyclic counter. Counts the number of AAL1 sequence errors i.e the

expected SC is not match with the received one (ESC!= RSC). See

Section 31.6, “3-Step-SN Algorithm

.”

0x06

Rx_SNP_Error

Hword

16-bit cyclic counter. Counts the number of ATM cell that received with

SNP error. (AAL1 PDU Header Error)

0x08

Rx_AAL1_SPE

Hword

16-bit cyclic counter. Counts the number of structured pointer error events

(i.e parity error, Tag cell or pointer mismatch). See

.”

0x0A

Rx_ReSYNC

Hword

16-bit cyclic counter. Counts the number of AAL1 resynchronized events:

pointer reframes, slip events, two consecutive cells with errors (SNE,

SCE, Tag…), and two consecutive pointers with errors (parity error or

pointer mismatch).

0x0C–

0x0E

—

Word

Reserved, should be cleared during initialization.