Table 19-8. valid sts/dts values for peripherals, 3 idma performance, Idma performance -23 – Freescale Semiconductor MPC8260 User Manual

Page 667: Valid sts/dts values for peripherals -23, Table 19-8, See table 19-8, Table 19-8. f

SDMA Channels and IDMA Emulation

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

19-23

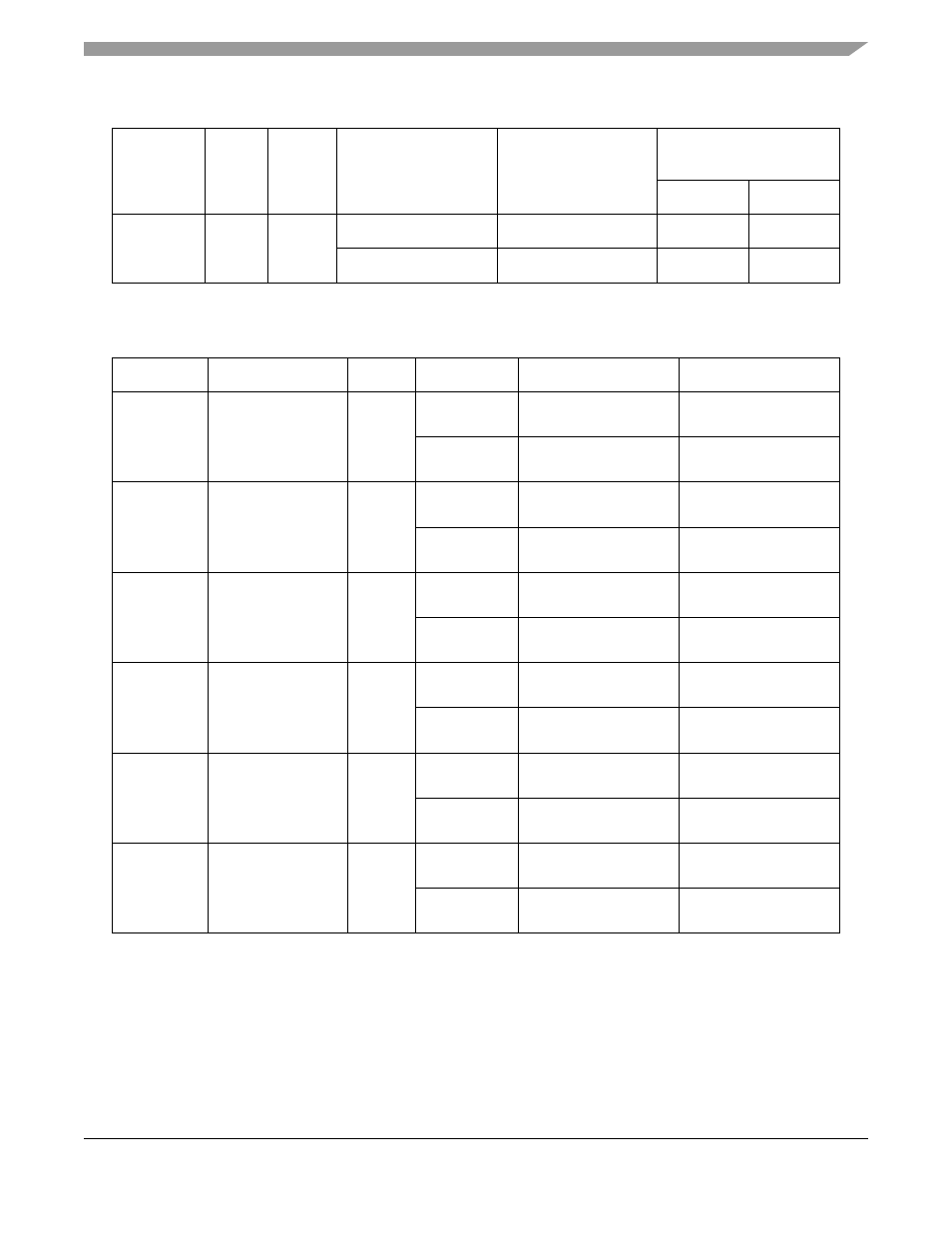

describes valid STS/DTS values for memory/peripheral operations.

19.8.3

IDMA Performance

The transfer parameters STS, DTS, SS_MAX, and DMA_WRAP determine the amount of data transferred

for each

START

_

IDMA

command issued. Using large internal IDMA transfer buffers and the maximum

101

2048

63 * 32

63 * 32

63 * 32, 9 * 32, 7 * 32, 32

1

1, 7, 9, 63

63 * 32, 9 * 32, 7 * 32, 32

63 * 32

1, 7, 9, 63

1

Table 19-8. Valid STS/DTS Values for Peripherals

DMA_WRAP

Internal Buffer Size SS_MAX

S/D Mode

STS (in Bytes)

DTS (in Bytes)

000

64

1 * 32

01

1 * 32

1, 2, 4, 8 (single)

1

; 32

(burst)

2

1

These values come out as a single transaction on the bus.

2

Peripherals that can accept bursts of 32 bytes are supported.

10

1, 2, 4, 8 (single); 32

(burst)

1 * 32

001

128

3 * 32

01

3 * 32

1, 2, 4, 8 (single); 32

(burst)

10

1, 2, 4, 8 (single); 32

(burst)

3 * 32

010

256

7 * 32

01

7 * 32

1, 2, 4, 8 (single); 32

(burst)

10

1, 2, 4, 8 (single); 32

(burst)

7 * 32

011

512

15 * 32

01

15 * 32

1, 2, 4, 8 (single); 32

(burst)

10

1, 2, 4, 8 (single); 32

(burst)

15 * 32

100

1024

31 * 32

01

31 * 32

1, 2, 4, 8 (single); 32

(burst)

10

1, 2, 4, 8 (single); 32

(burst)

31 * 32

101

2048

63 * 32

01

63 * 32

1, 2, 4, 8 (single); 32

(burst)

10

1, 2, 4, 8 (single); 32

(burst)

63 * 32

Table 19-7. Valid Memory-to-Memory STS/DTS Values

DMA_WRAP

Internal

Buffer

Size

SS_MAX

STS (in Bytes)

DTS (in Bytes)

Number of Transfers to Fill

Internal Buffer

STS Size

DTS Size