Table 9-66. dmamrx field descriptions (continued), Dmamrx field descriptions -89 – Freescale Semiconductor MPC8260 User Manual

Page 395

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-89

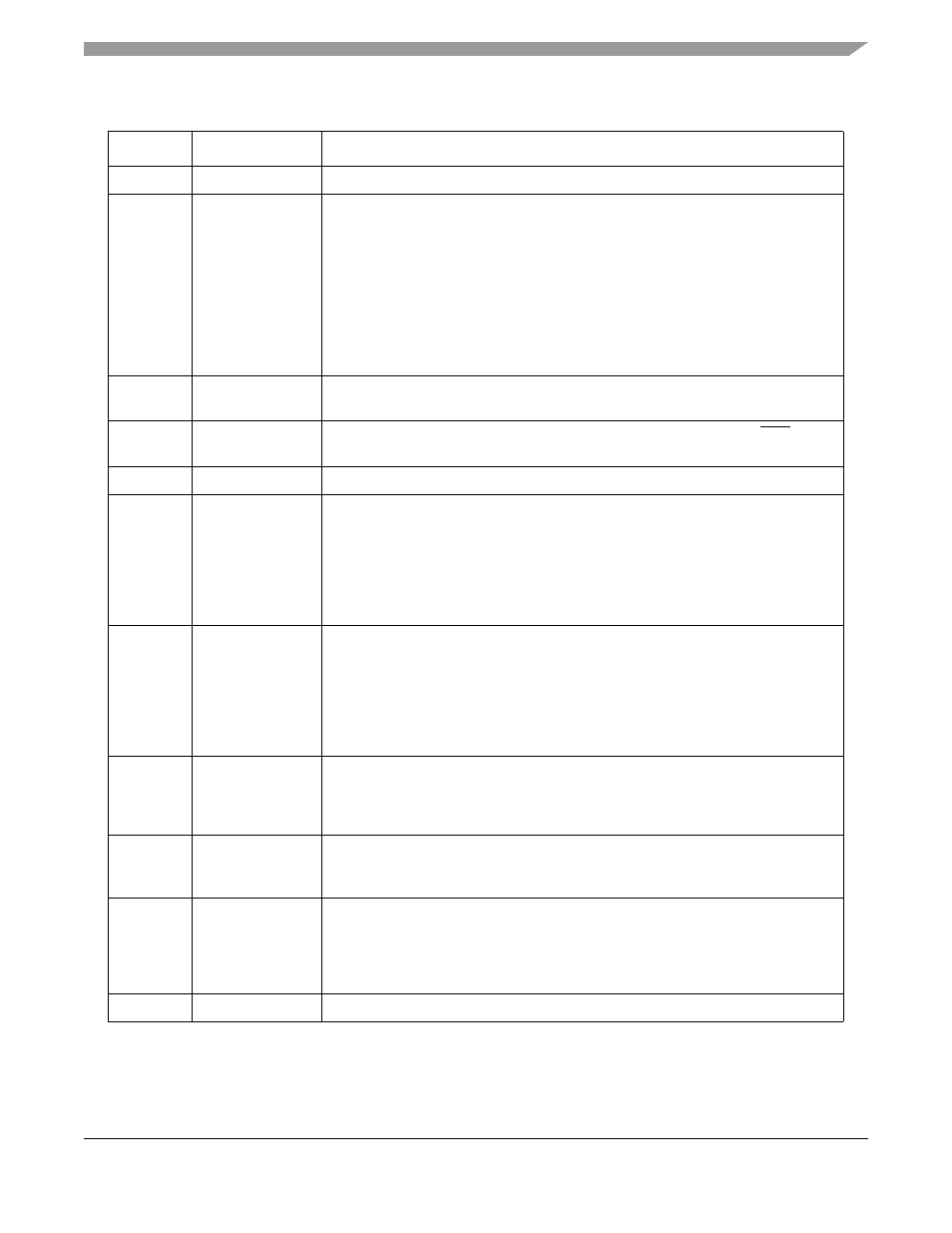

Table 9-66. DMAMR

x Field Descriptions

Bits

Name

Description

31–24

—

Reserved, should be cleared.

23–21

BWC

Bandwidth control. This field only applies when multiple channels are executing

transfers concurrently. The field determines how many cache lines a given Channel

is allowed to transfer after it is granted access to the

IOS

interface and before it

releases the interface to the next channel.

This allows the user to prioritize DMA

Channels.

000 1 cache line

001 2 cache lines

010 4 cache lines

011 8 cache lines

100 16 cache lines

20

DM_SEN

Direct mode snoop enable. When set allows snooping during direct mode DMA

transactions.

19

IRQS

Interrupt steer. When set routes all DMA interrupts to PCI bus through INTA. When

clear routes all DMA interrupts to local core.

18

—

Reserved, should be cleared.

17–16

DAHTS

Destination address hold transfer size. Indicates the transfer size used for each

transaction when DAHE is enabled. The Byte Count Register must be in multiples of

the size, and the Destination Address Register must be aligned based on the size.

00 1 byte

01 2 bytes

10 4 bytes

11 8 bytes

15–14

SAHTS

Source address hold transfer size. Indicates the transfer size used for each

transaction when SAHE is enabled. The Byte Count Register must be in multiples of

the size, and the Source Address Register must be aligned based on the size.

00 1 byte

01 2 bytes

10 4 bytes

11 -8 bytes

13

DAHE

Destination address hold enable. When set will allow the DMA controller to hold the

destination address constant for every transfer. The size used for transfer is

indicated by DAHTS. Note that hardware supports only aligned transfers for this

feature.

12

SAHE

Source address hold enable. When set will allow the DMA controller to hold the

source address constant for every transfer. The size used for the transfer is indicated

by SAHTS. Note that hardware supports only aligned transfers for this feature.

11–10

PRC

PCI read command. Indicates the types of PCI read command to use.

00 PCI read

01 PCI read line

10 PCI read multiple

11 Reserved

9–8

—

Reserved, should be cleared.