13 scc bisync transmit bd (txbd), Figure 23-7. scc bisync transmit bd (txbd), Scc bisync transmit bd (txbd) -14 – Freescale Semiconductor MPC8260 User Manual

Page 764

SCC BISYNC Mode

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

23-14

Freescale Semiconductor

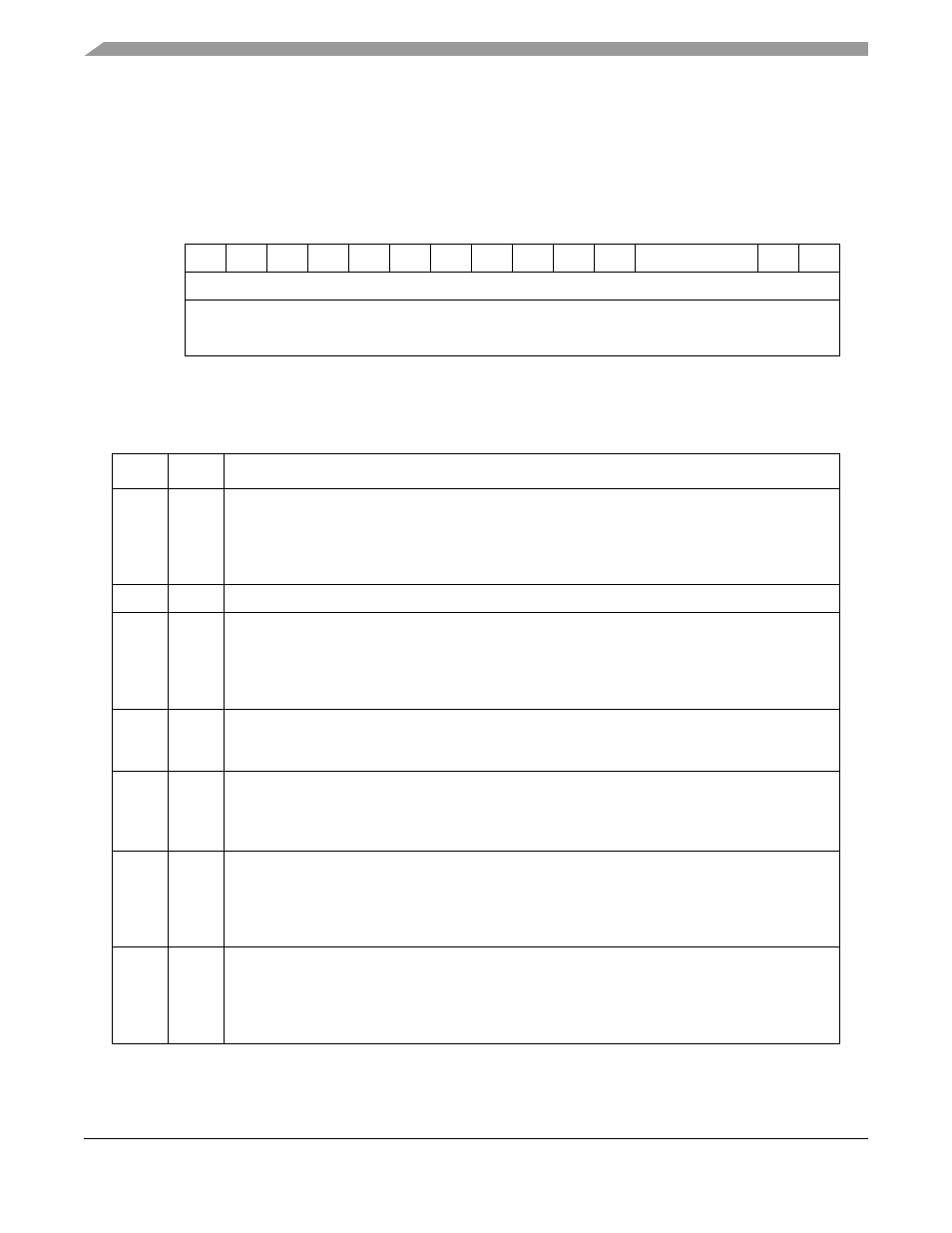

23.13 SCC BISYNC Transmit BD (TxBD)

The CP arranges data to be sent on an SCC channel in buffers referenced by the channel TxBD table. The

CP uses BDs to confirm transmission or indicate errors so the core knows buffers have been serviced. The

user configures status and control bits before transmission, but the CP sets them after the buffer is sent.

describes SCC BISYNC TxBD status and control fields.

0

1

2

3

4

5

6

7

8

9

10

11

13

14

15

Offset + 0

R

—

W

I

L

TB

CM

BR

TD

TR

B

—

UN

CT

Offset + 2

Data Length

Offset + 4

Tx Data Buffer Pointer

Offset + 6

Figure 23-7. SCC BISYNC Transmit BD (TxBD)

Table 23-12. SCC BISYNC TxBD Status and Control Field Descriptions

Bits

Name

Description

0

R

Ready.

0 The buffer is not ready for transmission. The current BD and buffer can be updated. The CP

clears R after the buffer is sent or after an error condition.

1 The user-prepared buffer has not been sent or is being sent. This BD cannot be updated while R

= 1.

1

—

Reserved, should be cleared.

2

W

Wrap (last BD in table).

0 Not the last BD in the table.

1 Last BD in the table. After this buffer is used, the CP sends data using the BD pointed to by

TBASE. The number of TxBDs in this table is determined only by the W bit and overall space

constraints of the dual-ported RAM.

3

I

Interrupt.

0 No interrupt is generated after this buffer is serviced.

1 SCCE[TXB] or SCCE[TXE] is set after the CP services this buffer, which can cause an interrupt.

4

L

Last in message.

0 The last character in the buffer is not the last character in the current block.

1 The last character in the buffer is the last character in the current block. The transmitter enters

and stays in normal mode after sending the last character in the buffer and the BCS, if enabled.

5

TB

Transmit BCS. Valid only when the L bit is set.

0 Send an SYN1–SYN2 or idle sequence (specified in GSMR[RTSM]) after the last character in the

buffer.

1 Send the BCS sequence after the last character. The controller also resets the BCS generator

after sending the BCS.

6

CM

Continuous mode.

0 Normal operation.

1 The CP does not clear R after this BD is closed, so the buffer is resent when the CP next

accesses this BD. However, R is cleared if an error occurs during transmission, regardless of how

CM is set.