Table 9-62. imisr field descriptions, Imisr field descriptions -81, Table 9-62 – Freescale Semiconductor MPC8260 User Manual

Page 387: Table 9-62 describes imisr fields

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-81

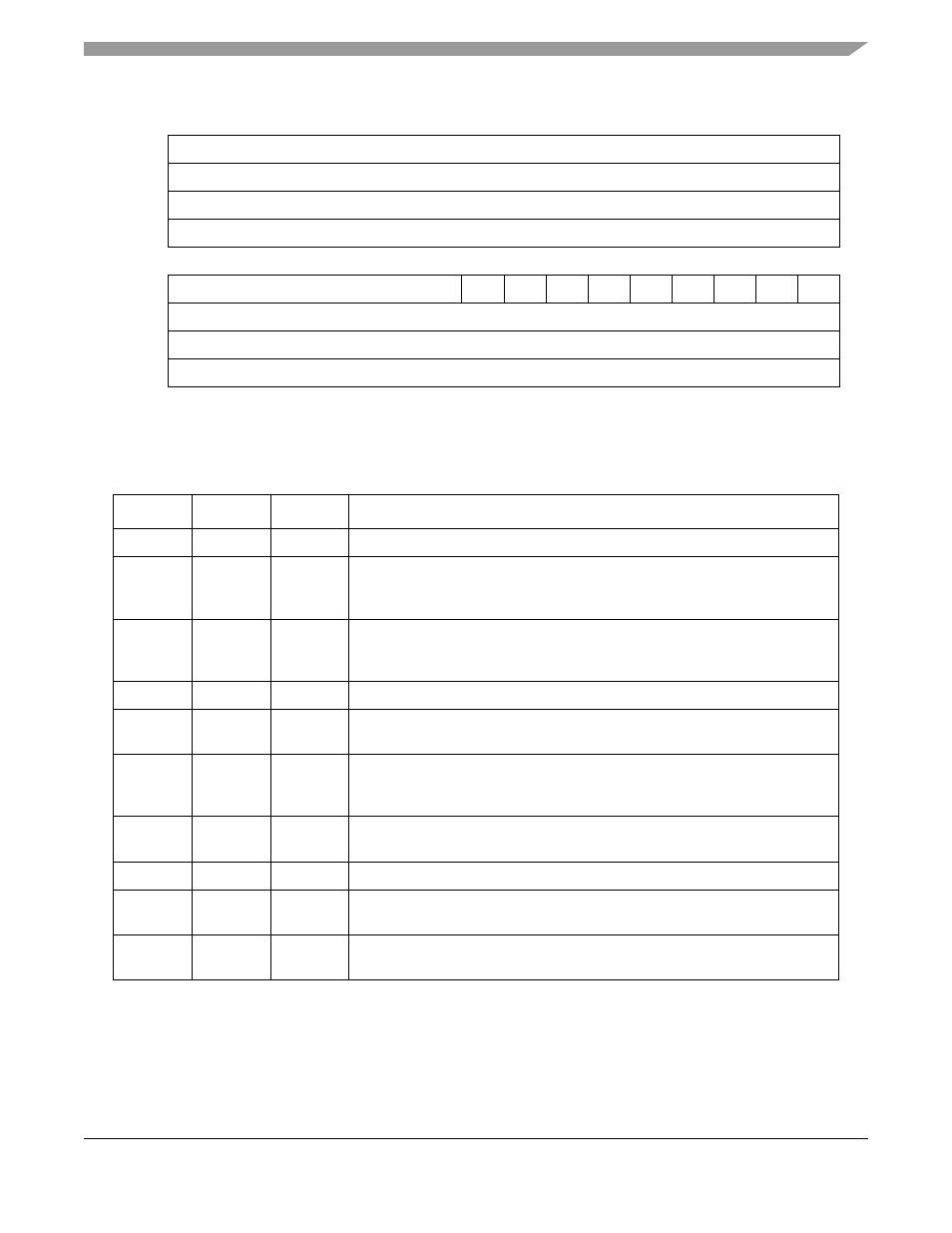

Figure 9-77. Inbound Message Interrupt Status Register (IMISR)

describes IMISR fields.

31

16

Field

—

Reset

0000_0000_0000_0000

R/W

.

Addr

0x10482

15

9

8

7

6

5

4

3

2

1

0

Field

—

OFOI IPOI

—

IPQI

MCI

IDI

—

IM1I

IM0I

Reset

0000_0000_0000_0000

R/W

.

Addr

0x10480

Table 9-62. IMISR Field Descriptions

Bits

Name

Access

Description

31–9

—

R

Reserved, should be cleared.

8

OFOI

R/Write 1

to clear

Outbound Free Overflow Interrupt. When set indicates that the Outbound

Free_FIFO Head pointer is equal to the Outbound Free_FIFO Tail pointer and

the queue is full. A machine check interrupt is generated.

7

IPOI

R/Write 1

to clear

Inbound Post Overflow Interrupt. When set indicates that the Inbound

Post_FIFO Head pointer is equal to the Inbound Post_FIFO Tail pointer and the

queue is full. A machine check interrupt is generated.

6

—

R

Reserved, should be cleared.

5

IPQI

R/Write 1

to clear

Inbound Post Queue Interrupt. When set indicates that the PCI master has

posted an MFA to the Inbound Post queue.

4

MCI

R

Machine check interrupt. When set indicates that a machine check interrupt

condition has been generated by setting the Inbound doorbell register’s bit 31.

The interrupt is cleared by resetting the Inbound doorbell register’s bit 31.

3

IDI

R

Inbound doorbell interrupt. When set indicates that there is an Inbound

Doorbell interrupt.

2

—

R

Reserved, should be cleared.

1

IM1I

R/Write 1

to clear

Inbound message 1 interrupt. When set indicates that there is an Inbound

message 1 interrupt.

0

IM0I

R/Write 1

to clear

Inbound message 0 interrupt. When set indicates that there is an Inbound

message 0 interrupt.