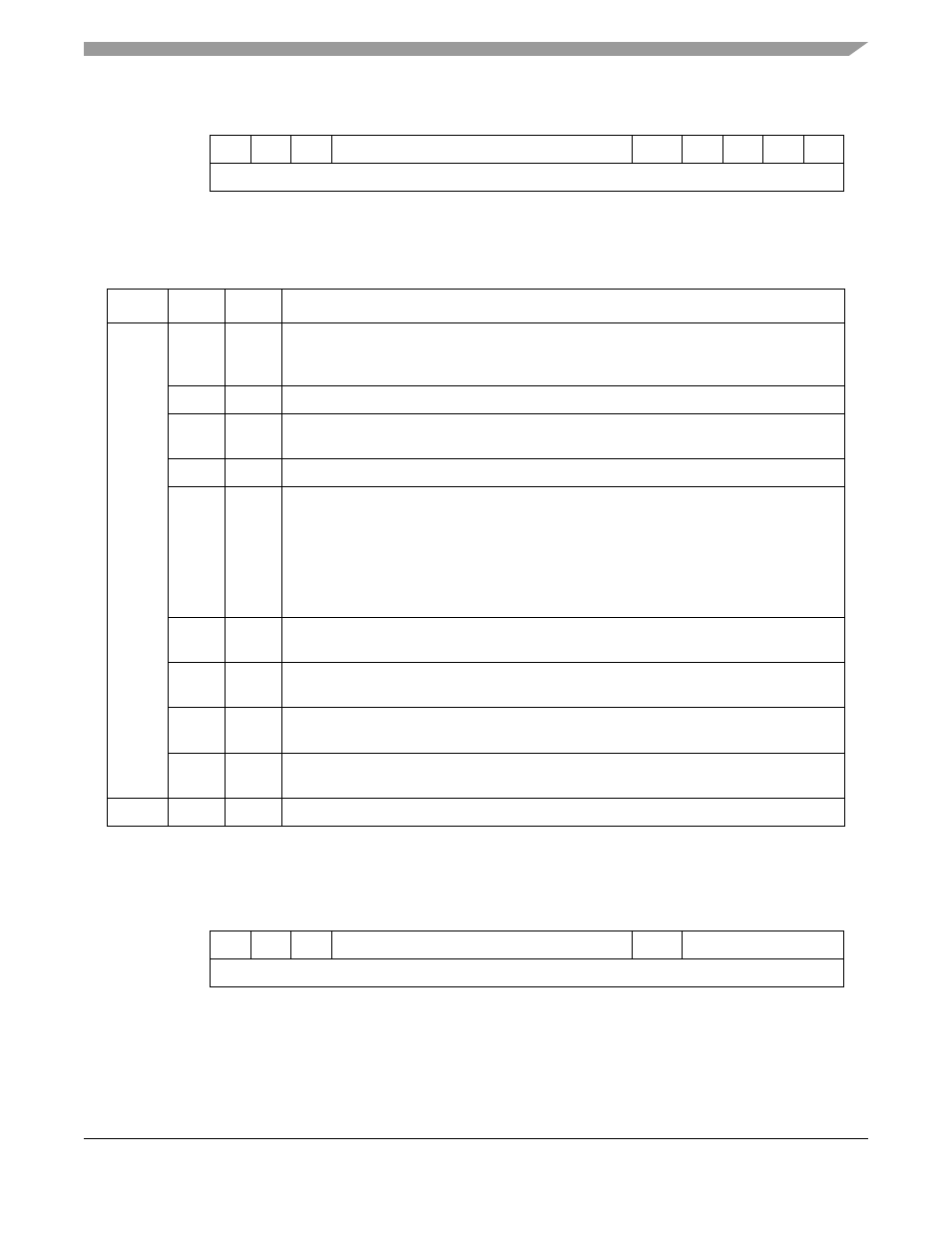

Figure 32-23. aal2 interrupt queue entry cid ¹ 0, Figure 32-24. aal2 interrupt queue entry cid = 0, Aal2 interrupt queue entry cid – Freescale Semiconductor MPC8260 User Manual

Page 1101: Aal2 interrupt queue entry cid = 0 -39, Hown in, Figure 32-23

ATM AAL2

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

32-39

describes the interrupt queue entry fields for a CID.

An interrupt entry for the VC is shown in

.

.

describes the interrupt queue entry fields for the VC. All the receive error events are enabled

by setting RCT[EM].

0

1

2

3

10

11

12

13

14

15

Offset + 0x00

V

—

W

CID

TBNR RXB BSY

TXB

RXF

Offset + 0x02

Channel Code (CC)

Figure 32-23. AAL2 Interrupt Queue Entry CID

≠ 0

Table 32-14. AAL2 Interrupt Queue Entry CID

≠ 0 Field Descriptions

Offset Bits

Name

Description

0x00

0

V

Valid interrupt entry

0 This interrupt queue entry is free and can be used by the CP.

1 This interrupt queue entry is valid. The host should read this interrupt and clear this bit.

1

—

—

2

W

Wrap bit. When set, this is the last interrupt entry in the circular table. During initialization,

the host must clear all W bits in the table except the last one, which must be set.

3–10

CID

CID number. The exception occurred for this CID.

11

TBNR

Tx buffer not ready interrupt. This interrupt is issued when the CP tries to open a TxBD,

which is not ready (R = 0). This interrupt is sent only if TxQD[BNM] = 1. The interrupt has

an associated channel code and CID.

Note: The CID number that is placed in the interrupt queue is the one currently located in

the last BD. Because the CID is not updated when the BD is not ready, the CID value

is the one extracted from this BD when it was last processed and transmitted. If the

BD is never processed and the BD was cleared, the CID value could be zero.

12

RXB

1

1

These interrupt queue fields are defined differently for other AAL types. Refer to

for more information.

Rx buffer interrupt. This interrupt is issued when the I bit is set for an RxBD and the

RxQD[RBM] bit is set. This interrupt has an associated channel code and CID.

13

BSY

Busy condition. The RxBD table associated with this channel’s CID is busy. Packets were

discarded due to this condition.

14

TXB

Transmit buffer interrupt. This interrupt is issued when the TxBD[I] bit is set. This interrupt

is sent only if TxQD[TBM] is set. This interrupt has an associated channel code and CID.

15

RXF

1

Receive SSSAR SDU (frame). An SSSAR frame belonging to this channel’s CID has been

received. This interrupt is sent only if RxQD[RFM]=1.

0x02

—

CC

Channel code specifies the ATM channel number associated with this interrupt.

0

1

2

3

10

11

12

15

Offset + 0x00

V

—

W

0000_0000

Error_Code

Offset + 0x02

Channel Code (CC)

Figure 32-24. AAL2 Interrupt Queue Entry CID = 0