5 i2c parameter ram, C parameter ram, The i – Freescale Semiconductor MPC8260 User Manual

Page 1273: C is inactive. table 39-6 shows the i

I

2

C Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

39-9

39.5

I

2

C Parameter RAM

The I

2

C controller parameter table is used for the general I

2

C parameters and is similar to the SCC

general-purpose parameter RAM. The CP accesses the I

2

C parameter table using a user-programmed

pointer (I2C_BASE) located in the parameter RAM; see

Section 14.5.2, “Parameter RAM.”

The I

2

C

parameter table can be placed at any 64-byte aligned address in the dual-port RAM’s general-purpose area

(banks 1–8, 11 and 12). The user must initialize certain parameter RAM values before the I

2

C is enabled;

the CP initializes the other values. Software usually does not access parameter RAM entries once they are

initialized; they should be changed only when the I

2

C is inactive.

shows the I

2

C parameter memory map.

1–6

—

Reserved and should be cleared.

7

M/S

Master/slave. Configures the I

2

C controller to operate as a master or a slave.

0 I

2

C is a slave.

1 I

2

C is a master.

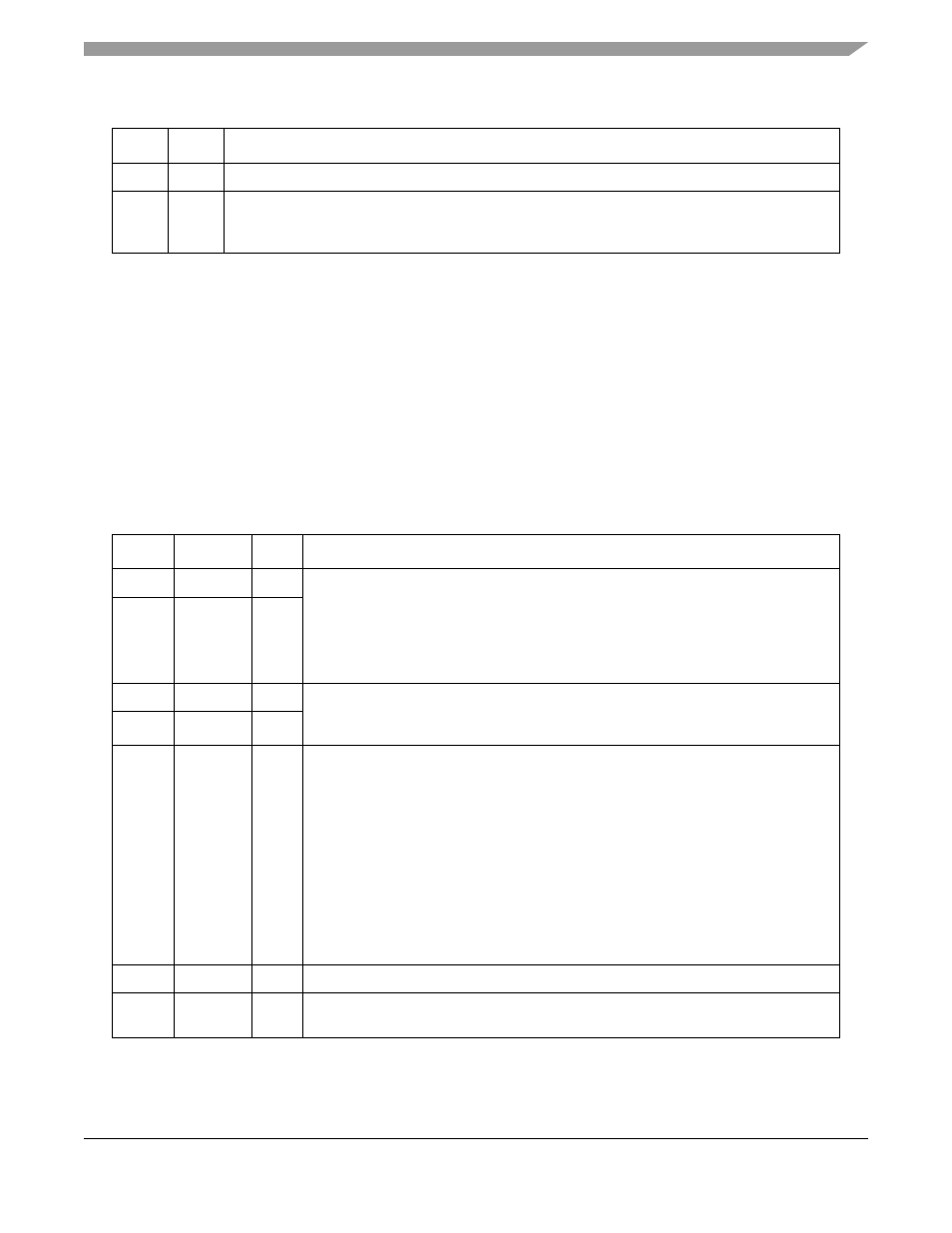

Table 39-6. I

2

C Parameter RAM Memory Map

Offset

1

Name

Width

Description

0x00

RBASE

Hword Rx/TxBD table base address. Indicate where the BD tables begin in the dual-port RAM.

Setting Rx/TxBD[W] in the last BD in each BD table determines how many BDs are

allocated for the Tx and Rx sections of the I

2

C. Initialize RBASE/TBASE before

enabling the I

2

C. Furthermore, do not configure BD tables of the I

2

C to overlap any

other active controller’s parameter RAM. RBASE and TBASE should be divisible by

eight.

0x02

TBASE

Hword

0x04

RFCR

Byte

Rx/Tx function code registers. The function code registers contain the transaction

specification associated with SDMA channel accesses to external memory. See

and

.

0x05

TFCR

Byte

0x06

MRBLR

Hword Maximum receive buffer length. Defines the maximum number of bytes the

PowerQUICC II writes to a Rx buffer before moving to the next buffer. The

PowerQUICC II writes fewer bytes to the buffer than the MRBLR value if an error or

end-of-frame occurs. Buffers should not be smaller than MRBLR.

Tx buffers are unaffected by MRBLR and can vary in length; the number of bytes to be

sent is specified in TxBD[Data Length].

MRBLR is not intended to be changed while the I

2

C is operating. However it can be

changed in a single bus cycle with one 16-bit move (not two 8-bit bus cycles

back-to-back). The change takes effect when the CP moves control to the next RxBD.

To guarantee the exact RxBD on which the change occurs, change MRBLR only while

the I

2

C receiver is disabled. MRBLR should be greater than zero; it should be an even

number if the character length of the data exceeds 8 bits.

0x08

RSTATE

Word

Rx internal state.

2

Reserved for CP use.

0x0C

RPTR

Word

Rx internal data pointer

2

is updated by the SDMA channels to show the next address

in the buffer to be accessed.

Table 39-5. I2COM Field Descriptions

Bits

Name Description