Figure 4-19. interrupt table handling example, 7 siu external interrupt control register (siexr), Interrupt table handling example -25 – Freescale Semiconductor MPC8260 User Manual

Page 197: Figure 4-19

System Interface Unit (SIU)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

4-25

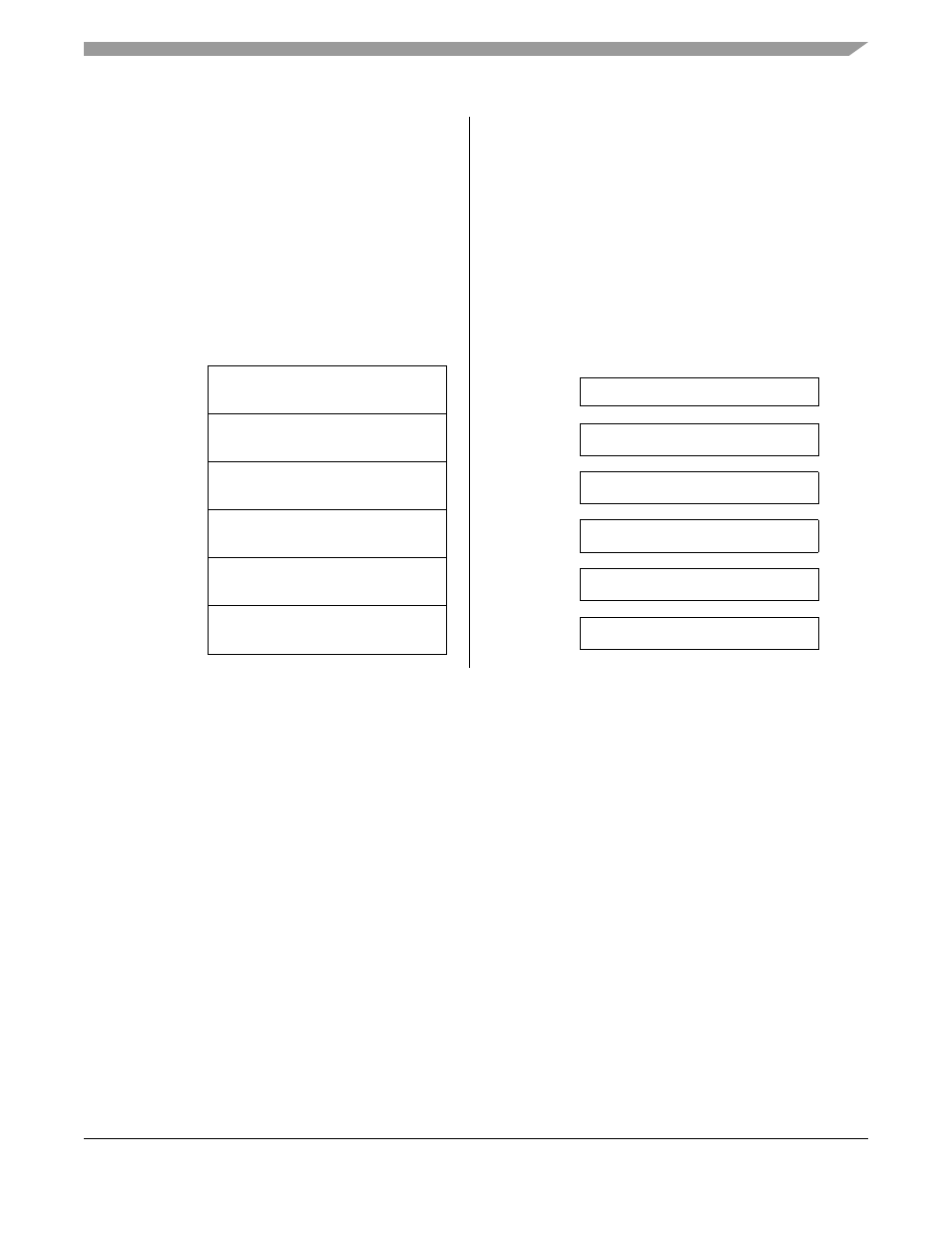

Figure 4-19. Interrupt Table Handling Example

NOTE

The PowerQUICC II differs from previous MPC8xx implementations in

that when an interrupt request occurs, SIVEC can be read. If there are

multiple interrupt sources, SIVEC latches the highest priority interrupt.

Note that the value of SIVEC cannot change while it is being read.

4.3.1.7

SIU External Interrupt Control Register (SIEXR)

Each defined bit in the SIU external interrupt control register (SIEXR), shown in

, determines

whether the corresponding port C line asserts an interrupt request upon either a high-to-low change or any

change on the pin. External interrupts can come from port C (PC[0-15]).

BASE

b Routine1

b Routine2

b Routine3

b Routine4

•

•

BASE + n

BASE + 4

BASE + 8

BASE + C

BASE +10

BASE

1st Instruction of Routine1

1st Instruction of Routine2

1st Instruction of Routine3

1st Instruction of Routine4

•

•

BASE + n

BASE + 400

BASE + 800

BASE + C00

BASE +1000

•

•

•

•

•

•

INTR: • • •

Save state

R3 <- @ SIVEC

R4 <-- BASE OF BRANCH TABLE

• • •

lbz

add

mtspr

bctr

RX, R3 (0)

# load as byte

RX, RX, R4

CTR, RX

INTR: • • •

Save state

R3 <- @ SIVEC

R4 <-- BASE OF BRANCH TABLE

• • •

lhz

add

mtspr

bctr

RX, R3 (0)

# load as half

RX, RX, R4

CTR, RX