Freescale Semiconductor MPC8260 User Manual

Page 162

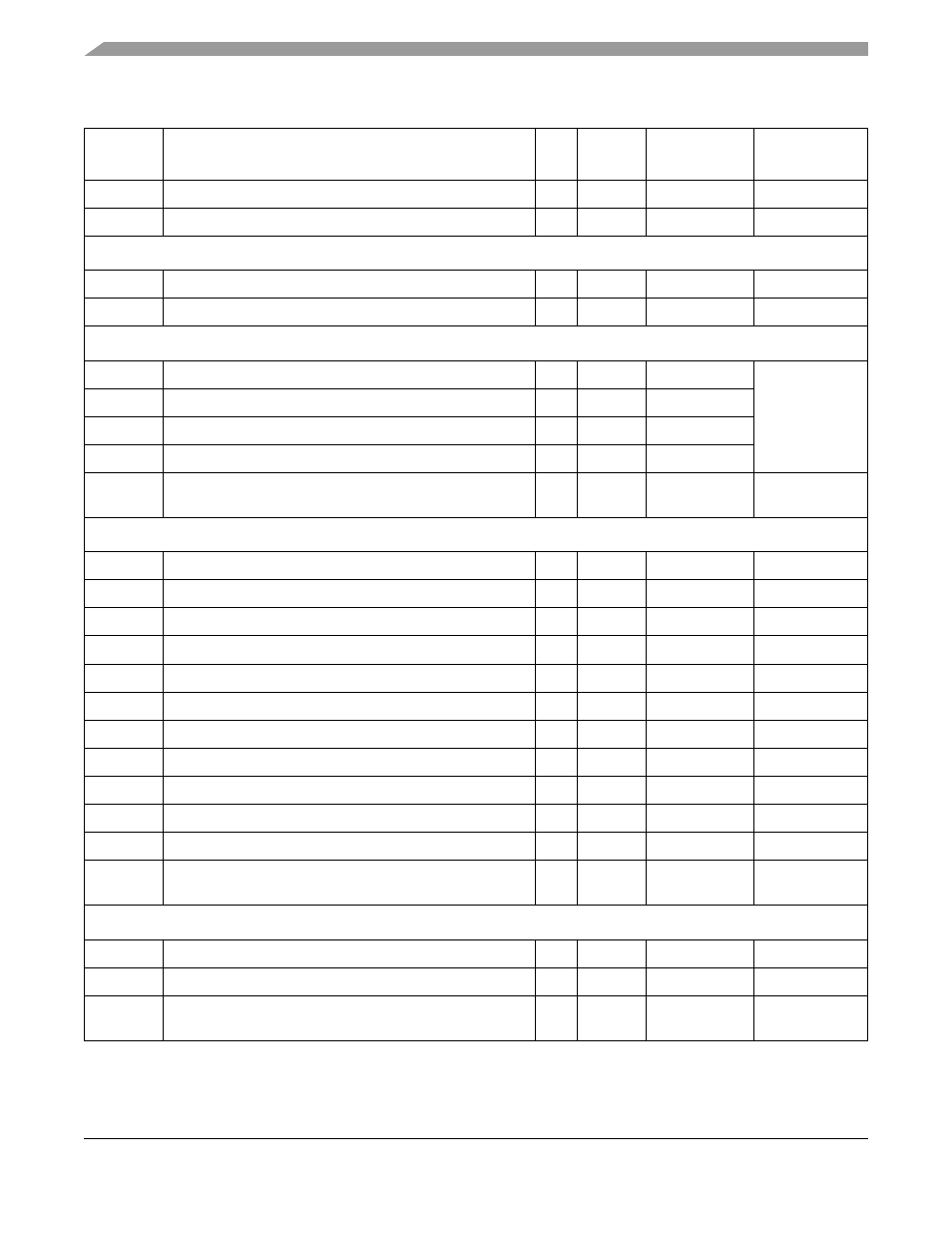

Memory Map

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

3-16

Freescale Semiconductor

0x114F2

TC8 error cells counter (TC_ECC8)

4

R/W

16 bits

0x0000

0x114F4

Reserved

—

12 bytes

—

—

TC Layer—General

4

0x11500

TC general status register (TCGSR)

4

R

16 bits

0x0000

0x11502

TC general event register (TCGER)

4

R/W

16 bits

0x0000

BRGs 5–8

0x115F0

BRG5 configuration register (BRGC5)

R/W

32 bits

0x0000_0000

0x115F4

BRG6 configuration register (BRGC6)

R/W

32 bits

0x0000_0000

0x1115F8

BRG7 configuration register (BRGC7)

R/W

32 bits

0x0000_0000

0x115FC

BRG8 configuration register (BRGC8)

R/W

32 bits

0x0000_0000

0x11600–

0x1185F

Reserved

—

608

bytes

—

—

I

2

C

0x11860

I

2

C mode register (I2MOD)

R/W

8 bits

0x00

0x11861

Reserved

—

24 bits

—

—

0x11864

I

2

C address register (I2ADD)

R/W

8 bits

0x00

0x11865

Reserved

—

24 bits

—

—

0x11868

I

2

C BRG register (I2BRG)

R/W

8 bits

0x00

0x11869

Reserved

—

24 bits

—

—

0x1186C

I

2

C command register (I2COM)

R/W

8 bits

0x00

0x1186D

Reserved

—

24 bits

—

—

0x11870

I

2

C event register (I2CER)

R/W

8 bits

0x00

0x11871

Reserved

—

24 bits

—

—

0x11874

I

2

C mask register (I2CMR)

R/W

8 bits

0x00

0x11875–

0x119BF

Reserved

—

315

bytes

—

—

Communications Processor

0x119C0

Communications processor command register (CPCR)

R/W

32 bits

0x0000_0000

0x119C4

CP configuration register (RCCR)

R/W

32 bits

0x0000_0000

0x119C8–

0x119D5

Reserved

—

14 bytes

—

—

Table 3-1. Internal Memory Map (continued)

Address

(offset)

Register

R/W

Size

Reset

Section/Page