1 message unit (i2o) registers, 2 dma controller registers, Message unit (i2o) registers -30 – Freescale Semiconductor MPC8260 User Manual

Page 336: Dma controller registers -30, 1 message unit (i, O) registers, Table 9-4. des cribes potar x

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-30

Freescale Semiconductor

9.11.1.1

Message Unit (I

2

O) Registers

Message unit registers are described in

Section 9.12, “Message Unit (I2O),” on page 9-65

9.11.1.2

DMA Controller Registers

DMA registers are described in

Section 9.13, “DMA Controller,” on page 9-85

.

9.11.1.3

PCI Outbound Translation Address Registers (POTAR

x)

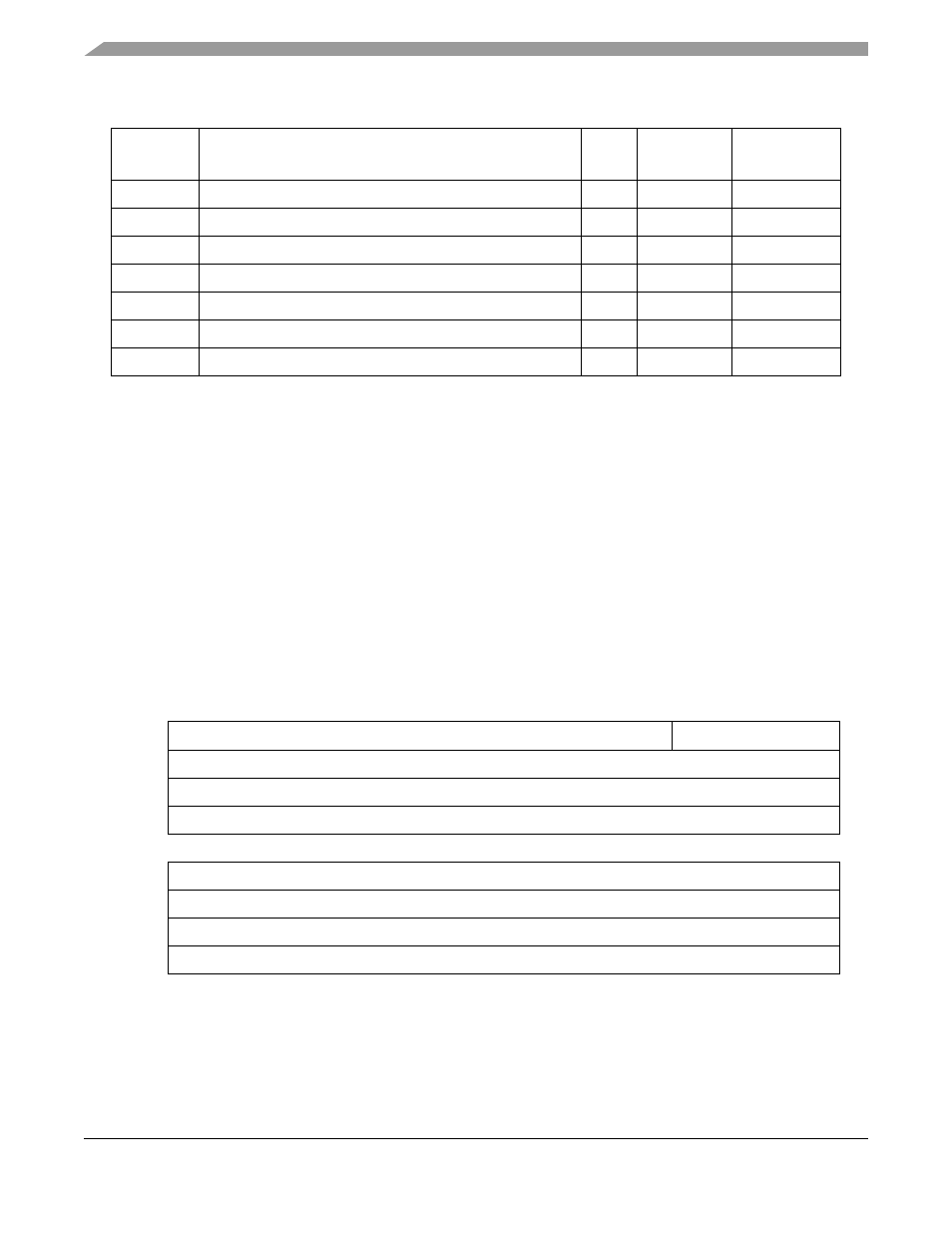

The PCI outbound translation address registers (POTARx), shown in

, select the starting

addresses in PCI address space for locally generated transactions that hit within the outbound translation

windows. The new translated address is created by concatenating the transaction offset to this translation

address. Refer to

Section 9.10.2.2, “PCI Outbound Translation.”

Figure 9-17. PCI Outbound Translation Address Registers (POTAR

x)

Table 9-4. describes POTARx.

0x108E0

PCI inbound comparison mask register 1 (PICMR1)

R/W

0x0000_0000

0x108E8

PCI inbound translation address register 0 (PITAR0)

R/W

0x0000_0000

0x108F0

PCI inbound base address register 0 (PIBAR0)

R/W

0x0000_0000

0x108F8

PCI inbound comparison mask register 0 (PICMR0)

R/W

0x0000_0000

0x10900

PCI CFG_ADDR

R/W

undefined

0x10904

PCI CFG_DATA

R/W

0x0000_0000

0x10908

PCI INT_ACK

R/W

undefined

31

20

19

16

Field

—

TA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10802 (POTAR0); 0x1081A (POTAR1); 0x10832 (POTAR2)

15

0

Field

TA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10800 (POTAR0); 0x10818 (POTAR1); 0x10830 (POTAR2)

Table 9-3. Internal Memory Map (continued)

Address

(offset)

Register

Access

Reset

Section/Page