Freescale Semiconductor MPC8260 User Manual

Page 152

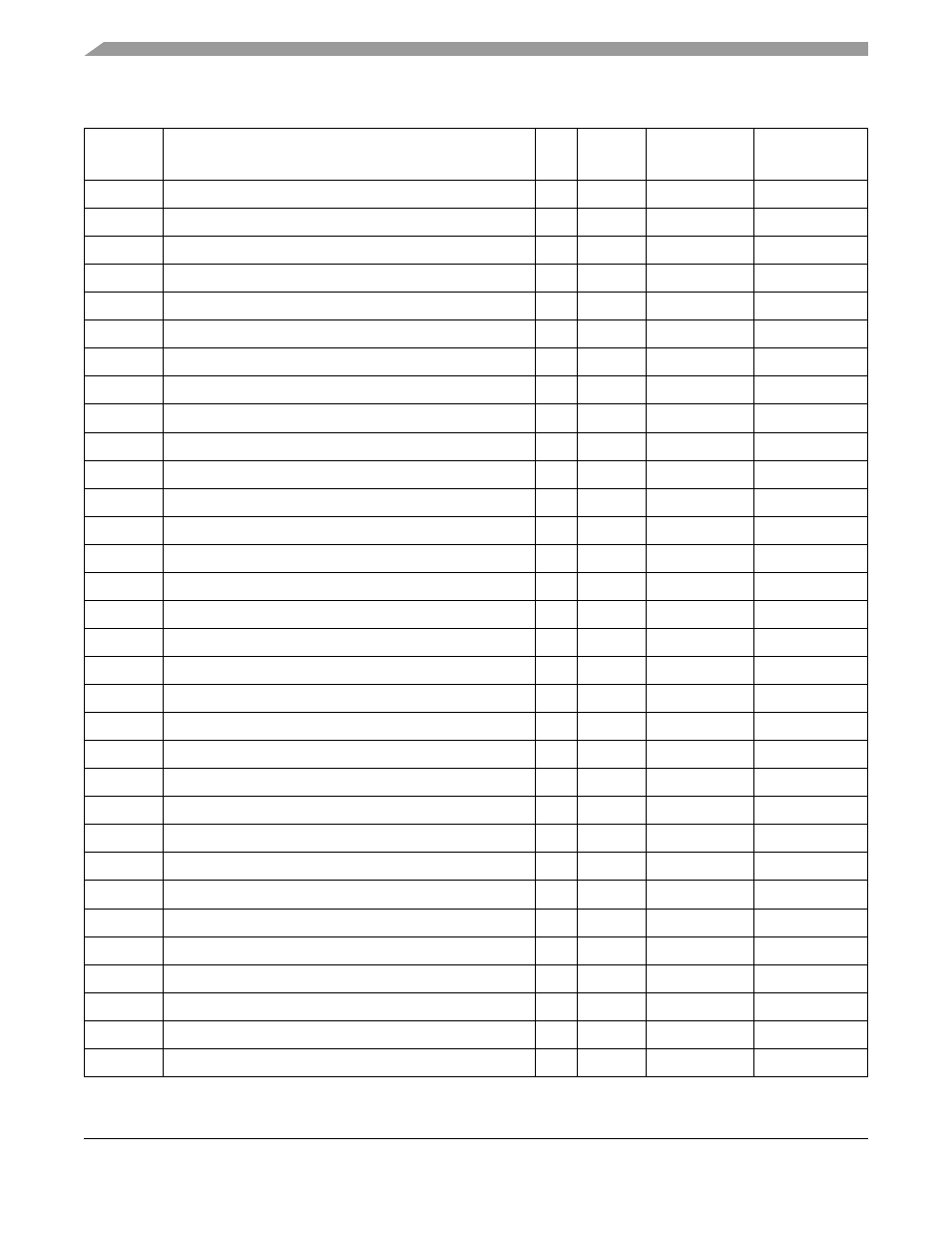

Memory Map

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

3-6

Freescale Semiconductor

0x10608

DMA 2 current descriptor address register (DMACDAR2)

2

R/W

32 bits

0x0000_0000

0x10610

DMA 2 source address register (DMASAR2)

2

R/W

32 bits

0x0000_0000

0x10618

DMA 2 destination address register (DAR2)

2

R/W

32 bits

0x0000_0000

0x10620

DMA 2 byte count register (DMABCR2)

2

R/W

32 bits

0x0000_0000

0x10624

DMA 2 next descriptor address register (DMANDAR2)

2

R/W

32 bits

0x0000_0000

0x10680

DMA 3 mode register (DMAMR3)

2

R/W

32 bits

0x0000_0000

0x10684

DMA 3 status register (DMASR3)

2

R/W

32 bits

0x0000_0000

0x10688

DMA 3 current descriptor address register (DMACDAR3)

2

R/W

32 bits

0x0000_0000

0x10690

DMA 3 source address register (DMASAR3)

2

R/W

32 bits

0x0000_0000

0x10698

DMA 3 destination address register (DMADAR3)

2

R/W

32 bits

0x0000_0000

0x106A0

DMA 3 byte count register (DMABCR3)

2

R/W

32 bits

0x0000_0000

0x106A4

DMA 3 next descriptor address register (DMANDAR3)

2

R/W

32 bits

0x0000_0000

0x10800

PCI outbound translation address register 0 (POTAR0)

2

R/W

32 bits

0x0000_0000

0x10808

PCI outbound base address register 0 (POBAR0)

2

R/W

32 bits

0x0000_0000

0x10810

PCI outbound comparison mask register 0 (POCMR0)

2

R/W

32 bits

0x0000_0000

0x10818

PCI outbound translation address register 1 (POTAR1)

2

R/W

32 bits

0x0000_0000

0x10820

PCI outbound base address register 1 (POBAR1)

2

R/W

32 bits

0x0000_0000

0x10828

PCI outbound comparison mask register 1 (POCMR1)

2

R/W

32 bits

0x0000_0000

0x10830

PCI outbound translation address register 2 (POTAR2)

2

R/W

32 bits

0x0000_0000

0x10838

PCI outbound base address register 2 (POBAR2)

2

R/W

32 bits

0x0000_0000

0x10840

PCI outbound comparison mask register 2 (POCMR2)

2

R/W

32 bits

0x0000_0000

0x10878

Discard timer control register (PTCR)

2

R/W

32 bits

0x0000_0000

0x1087C

General purpose control register (GPCR)

2

R/W

32 bits

0x0000_0000

0x10880

PCI general control register (PCI_GCR)

2

R/W

32 bits

0x0000_0000

0x10884

Error status register (ESR)

2

R/W

32 bits

0x0000_0000

0x10888

Error mask register (EMR)

2

R/W

32 bits

0x0000_0FFF

0x1088C

Error control register (ECR)

2

R/W

32 bits

0x0000_00FF

0x10890

PCI error address capture register (PCI_EACR)

2

R/W

32 bits

0x0000_0000

0x10898

PCI error data capture register (PCI_EDCR)

2

R/W

32 bits

0x0000_0000

0x108A0

PCI error control capture register (PCI_ECCR)

2

R/W

32 bits

0x0000_0000

0x108D0

PCI inbound translation address register 1 (PITAR1)

2

R/W

32 bits

0x0000_0000

0x108D8

PCI inbound base address register 1 (PIBAR1)

2

R/W

32 bits

0x0000_0000

Table 3-1. Internal Memory Map (continued)

Address

(offset)

Register

R/W

Size

Reset

Section/Page