1 hdlc bus features, 2 accessing the hdlc bus, Hdlc bus features -18 – Freescale Semiconductor MPC8260 User Manual

Page 746: Accessing the hdlc bus -18, Typical hdlc bus single-master configuration -18

SCC HDLC Mode

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

22-18

Freescale Semiconductor

In single-master configuration, a master station transmits to any slave station without collisions. Slaves

communicate only with the master, but can experience collisions in their access over the bus. In this

configuration, a slave that communicates with another slave must first transmit its data to the master, where

the data is buffered in RAM and then resent to the other slave. The benefit of this configuration, however,

is that full-duplex operation can be obtained. In a point-to-multipoint environment, this is the preferred

configuration.

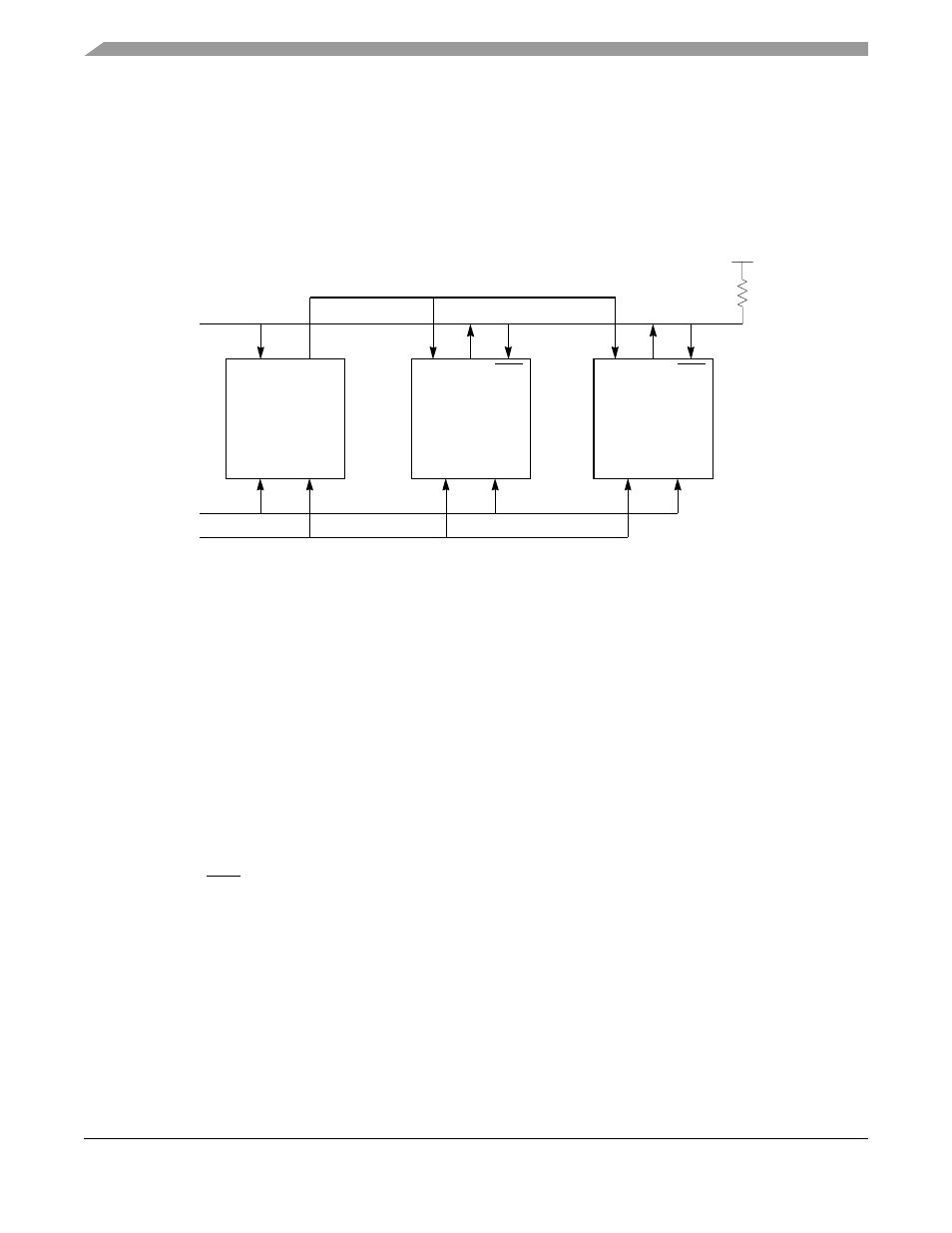

shows the single-master configuration.

Figure 22-11. Typical HDLC Bus Single-Master Configuration

22.15.1 HDLC Bus Features

The main features of the HDLC bus are as follows:

•

Superset of the HDLC controller features

•

Automatic HDLC bus access

•

Automatic retransmission in case of collision

•

May be used with the NMSI or a TDM bus

•

Delayed RTS mode

22.15.2 Accessing the HDLC Bus

The HDLC bus protocol ensures orderly bus control when multiple transmitters attempt simultaneous

access. The transmitter sending a zero bit at the time of collision completes the transmission. If a station

sends out an opening flag (0x7E) while another station is already sending, the collision is always detected

within the first byte, because the transmission in progress is using zero bit insertion to prevent flag

imitation.

HDLC

Controller

RXD

TXD

A

RCLK

HDLC Bus

Controller

RXD

CTS

TXD

B

HDLC Bus

Controller

RXD

CTS

TXD

C

Clock1

HDLC Bus LAN

+ 3.3 V

R

Slave

Slave

Master

NOTES:

1. Transceivers may be used to extend the LAN size.

2. The TXD pins of slave devices should be configured to open-drain in the port C parallel I/O port.

3. Clock1 is the master RCLK and the slave TCLK.

Clock2

TCLK

RCLK

TCLK

RCLK

TCLK

4. Clock2 is the master TCLK and the slave RCLK.