23 pci bus arbiter configuration register, Pci bus arbiter configuration register -59, Pci bus function register field descriptions -59 – Freescale Semiconductor MPC8260 User Manual

Page 365: Section 9.11.2.23, “pci, Bus arbiter configuration register

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-59

9.11.2.23 PCI Bus Arbiter Configuration Register

The PCI bus arbiter configuration register, shown in

, is used to determine the configuration of

the PCI bus arbiter. Only 1-byte or 2-byte accesses to address offset 0x46 are allowed.

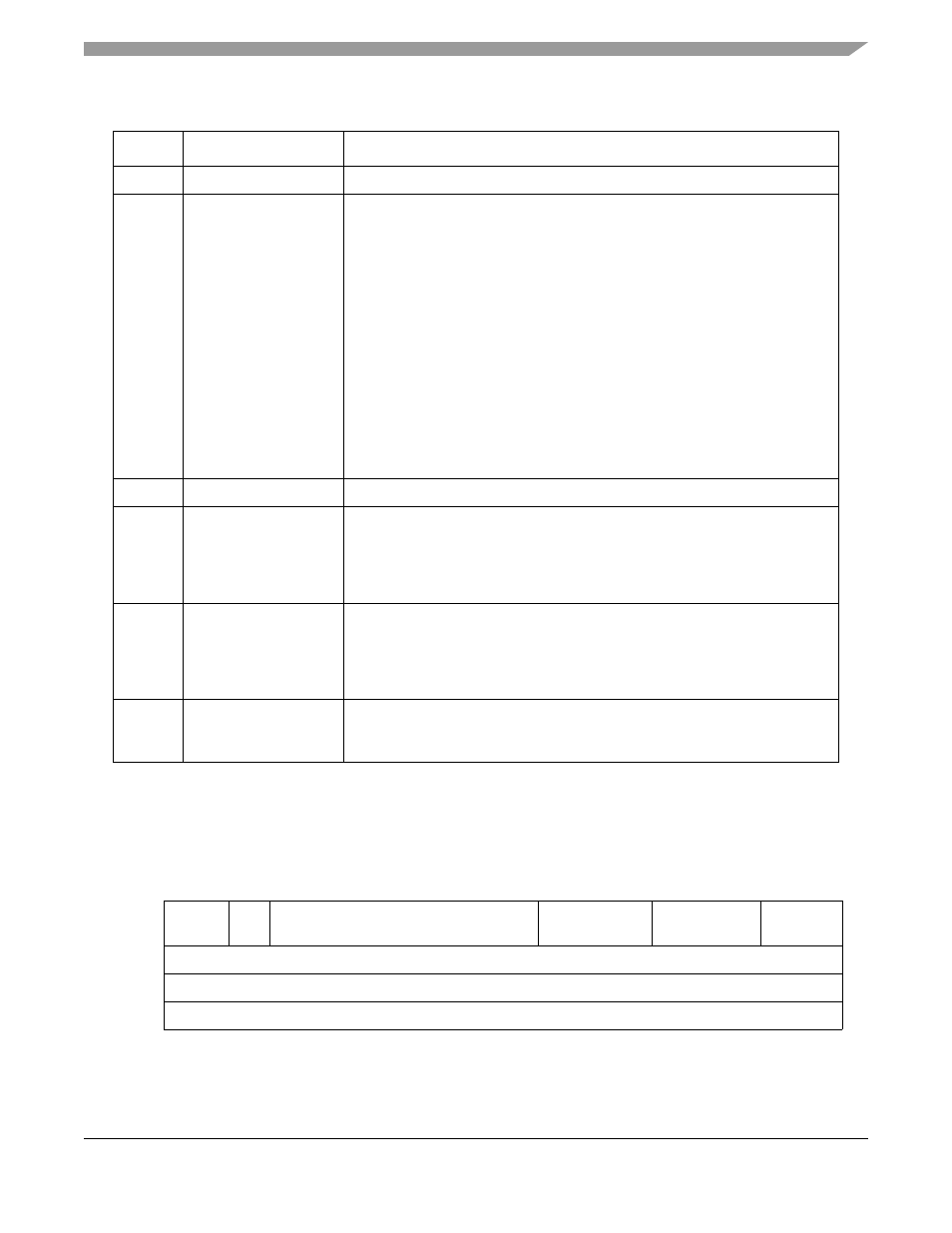

Figure 9-55. PCI Bus Arbiter Configuration Register

Table 9-41. PCI Bus Function Register Field Descriptions

Bits

Name

Description

15–6

—

Reserved, should be cleared.

5

CFG_LOCK

Agent mode: Setting CFG_LOCK prevents an external PCI master from

accessing the configuration space while the 60x bus is doing internal

configuration. It is explicitly set and cleared by the 60x bus.

0 PCI bridge accepts accesses to the PCI configuration space or the internal

memory-mapped configuration space.

1 PCI bridge retries all accesses to the PCI configuration space or the internal

memory-mapped configuration space.

Host mode: the PCI configuration space is not accessible from the PCI side

when the device is in host mode; therefore, this bit applies only for the internal

memory-mapped configuration space.

0 PCI bridge accepts accesses to the internal memory-mapped configuration

space.

1 PCI bridge retries all accesses to the internal memory-mapped configuration

space.

4-3

—

Reserved, should be cleared.

2

TRGT_LATENCY_DIS

Target latency time-out disable. Controls whether the PCI bridge as a target

time-outs when the first data phase of a transaction has not completed in 16 PCI

cycles.

0 Target latency time-out enabled.

1 Target latency time-out disabled.

1

MSTR_LATENCY_DIS

Master latency timer disable. Controls whether the PCI bridge as a master ends

a transaction after the expiration of the master latency timer. See

Section 9.11.2.10, “PCI Bus Latency Timer Register

0 Master latency timer enabled.

1 Master latency timer disabled.

0

PCI_HA

Set or cleared by a Power-On configuration bit on power-up and is read-only.

0 PCI interface is in host mode

1 PCI interface is in agent mode

15

14

13

7

6

4

3

1

0

Field

PCI_

ARB_DIS

PM

—

PCI_BUSMP

—

PCI_

BRIDGE MP

Reset

0

1

000_0000_0000_0000

1

Reset value determined by PIC_CFG[1] pin value after hard reset. Refer to

R/W

R/W

Addr

0x46