6 interrupts from port c, Interrupts from port c -19 – Freescale Semiconductor MPC8260 User Manual

Page 1297

Parallel I/O Ports

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

40-19

40.6

Interrupts from Port C

The port C lines associated with CDx and CTSx have a mode of operation where the pin can be internally

connected to the SCC/FCC but can also generate interrupts. Port C still detects changes on the CTS and

CD pins and asserts the corresponding interrupt request, but the SCC/FCC simultaneously uses CTS

PD11

TDMB2: L1RQ

FCC2: RxD[0]

1,4

UTOPIA 8

(secondary option)

GND

TDM_B1:

L1TSYNC/GRANT

GND

PD10

TDMB2: L1CLKO

FCC2: RxD[1]

1,4

UTOPIA 8

(secondary option)

GND

BRG4: BRGO

TDM_B1: L1RSYNC

GND

PD9

SMC1: SMTXD

BRG3: BRGO

FCC2: RxPrty

1

UTOPIA

GND

PD8

FCC2: TxPrty

1

UTOPIA

SMC1: SMRXD

GND

BRG5: BRGO

PD7

SMC1: SMSYN

GND

FCC1: TxAddr[3]

1,2

MPHY, master,

multiplexed polling

FCC2: TxAddr[4]

1

MPHY, master,

multiplexed polling

FCC1: TxAddr[3]

1,3

MPHY, slave,

multiplexed polling

FCC1: TxClav2

1,3

MPHY, master, direct

polling

FCC2: TxAddr[1]

1

MPHY, slave,

multiplexed polling

GND

PD6

FCC1: TxD[4]

1

UTOPIA 16

IDMA1: DACK

PD5

FCC1: TxD[3]

1

UTOPIA 16

IDMA1: DONE

4

Inout

(secondary option)

V

DD

PD4

BRG8: BRGO

TDM_D1:

L1TSYNC/GRANT

4

(secondary option)

GND

FCC3: RTS

SMC2: SMRXD

4

(secondary option)

GND

1

Not available on the MPC8250.

2

MPHY address pins 3 and 4 (master mode) can come from FCC2, depending on CMXUAR programming. (See

Section 16.4.1, “CMX UTOPIA Address Register (CMXUAR)

.”)

3

MPHY address pins 0–4 (slave mode) can come from FCC2, depending on CMXUAR programming. (See

Section 16.4.1, “CMX UTOPIA Address Register (CMXUAR)

.”)

4

Available only when the primary option for this function is not used.

5

.25

µm (HiP4) devices only: primary option.

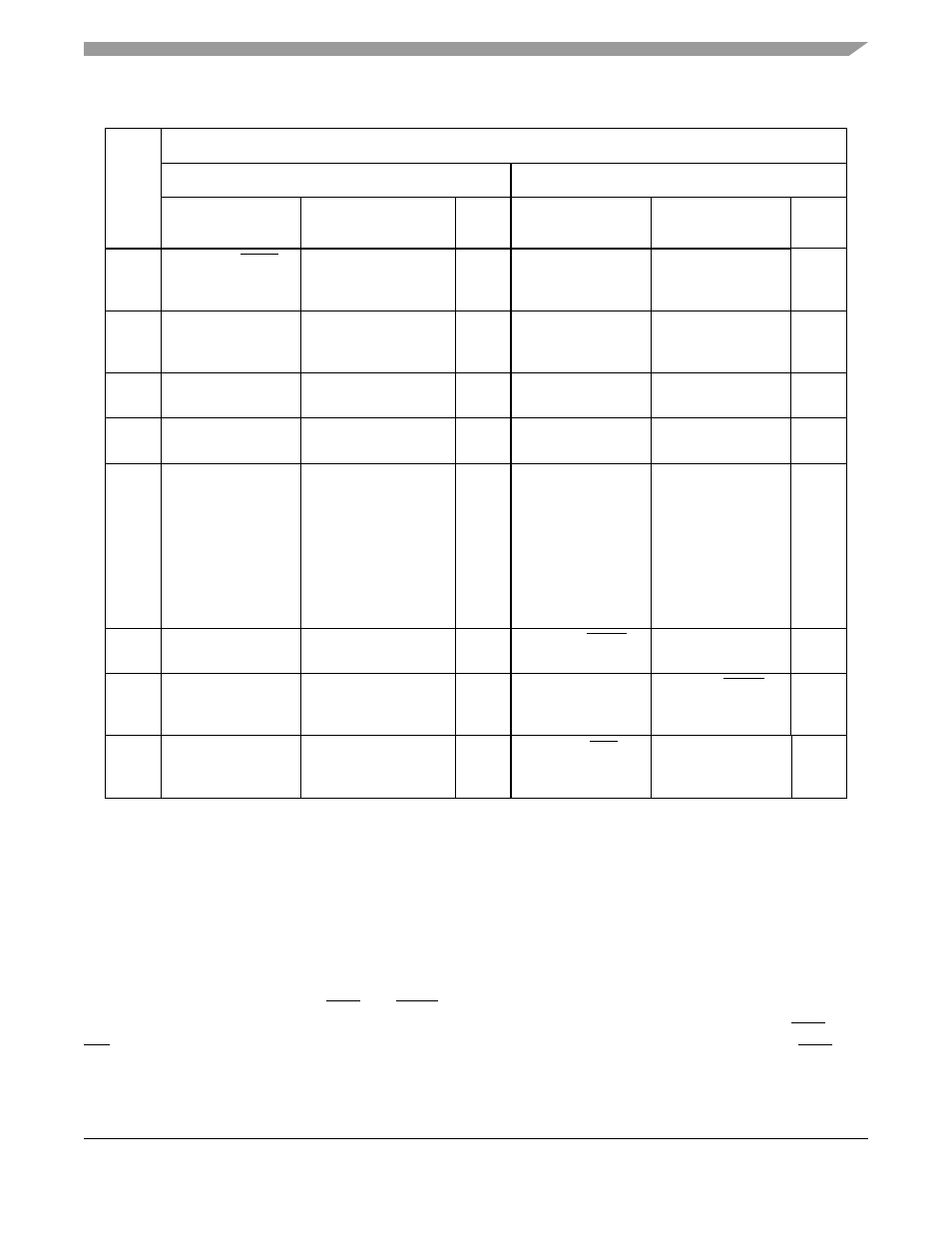

Table 40-8. Port D Dedicated Pin Assignment (PPARD = 1) (continued)

Pin

Pin Function

PSORD = 0

PSORD = 1

PDIRD = 1 (Output)

PDIRD = 0 (Input)

Defaul

t Input

PDIRD = 1 (Output)

PDIRD = 0 (Input, or

Inout if Specified)

Defaul

t Input