Freescale Semiconductor MPC8260 User Manual

Page 696

Serial Communications Controllers (SCCs)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

20-18

Freescale Semiconductor

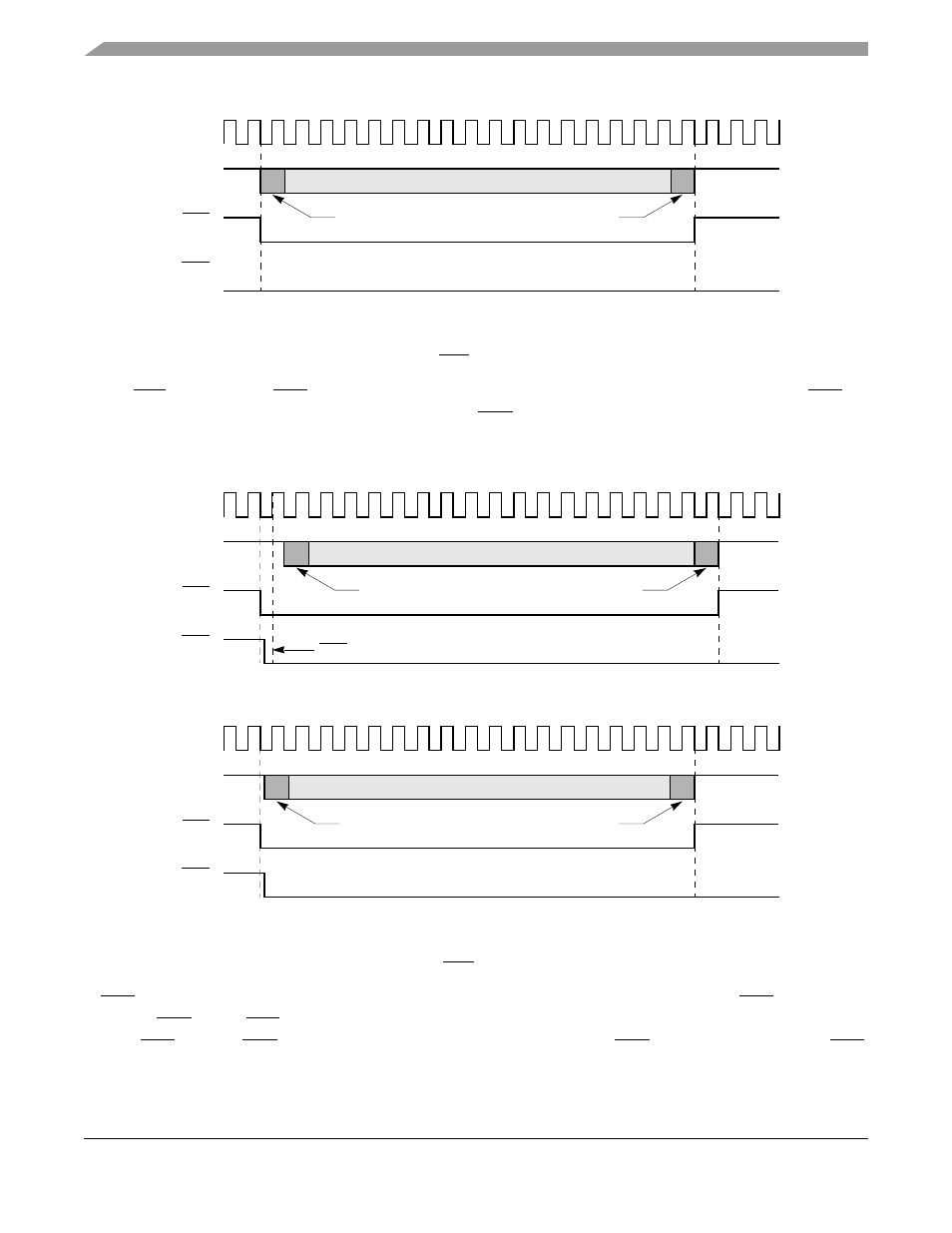

Figure 20-9. Output Delay from RTS Asserted for Synchronous Protocols

When RTS is asserted, if CTS is not already asserted, delays to the first data bit depend on when CTS is

asserted.

shows that the delay between CTS and the data can be approximately 0.5 to 1 bit

times or no delay, depending on GSMR_H[CTSS].

Figure 20-10. Output Delay from CTS Asserted for Synchronous Protocols

If CTS is programmed to envelope data, negating it during frame transmission causes a CTS lost error.

Negating CTS forces RTS high and Tx data to become idle. If GSMR_H[CTSS] is zero, the SCC must

sample CTS before a CTS lost is recognized; otherwise, the negation of CTS immediately causes the CTS

lost condition. See

1. A frame includes opening and closing flags and syncs, if present in the protocol.

TCLK

TXD

Last Bit of Frame Data

First Bit of Frame Data

NOTE:

(Output)

RTS

(Output)

CTS

(Input)

1. GSMR_H[CTSS] = 0. CTSP is a don’t care.

TCLK

TXD

Last Bit of Frame Data

First Bit of Frame Data

NOTE:

CTS Sampled Low Here

1. GSMR_H[CTSS] = 1. CTSP is a don’t care.

TCLK

TXD

Last Bit of Frame Data

First Bit of Frame Data

NOTE:

(Output)

RTS

(Output)

CTS

(Input)

(Output)

RTS

(Output)

CTS

(Input)