3 reset mode register (rmr), Figure 5-3. reset mode register (rmr), Reset mode register (rmr) -5 – Freescale Semiconductor MPC8260 User Manual

Page 227: Table 5-4 des cribes rmr fields

Reset

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

5-5

NOTE

The Reset Status Register accumulates reset events. For example, because

software watchdog expiration results in a hard reset, which in turn results in

a soft reset, RSR[SWRS], RSR[ESRS] and RSR[EHRS] are all set after a

software watchdog reset.

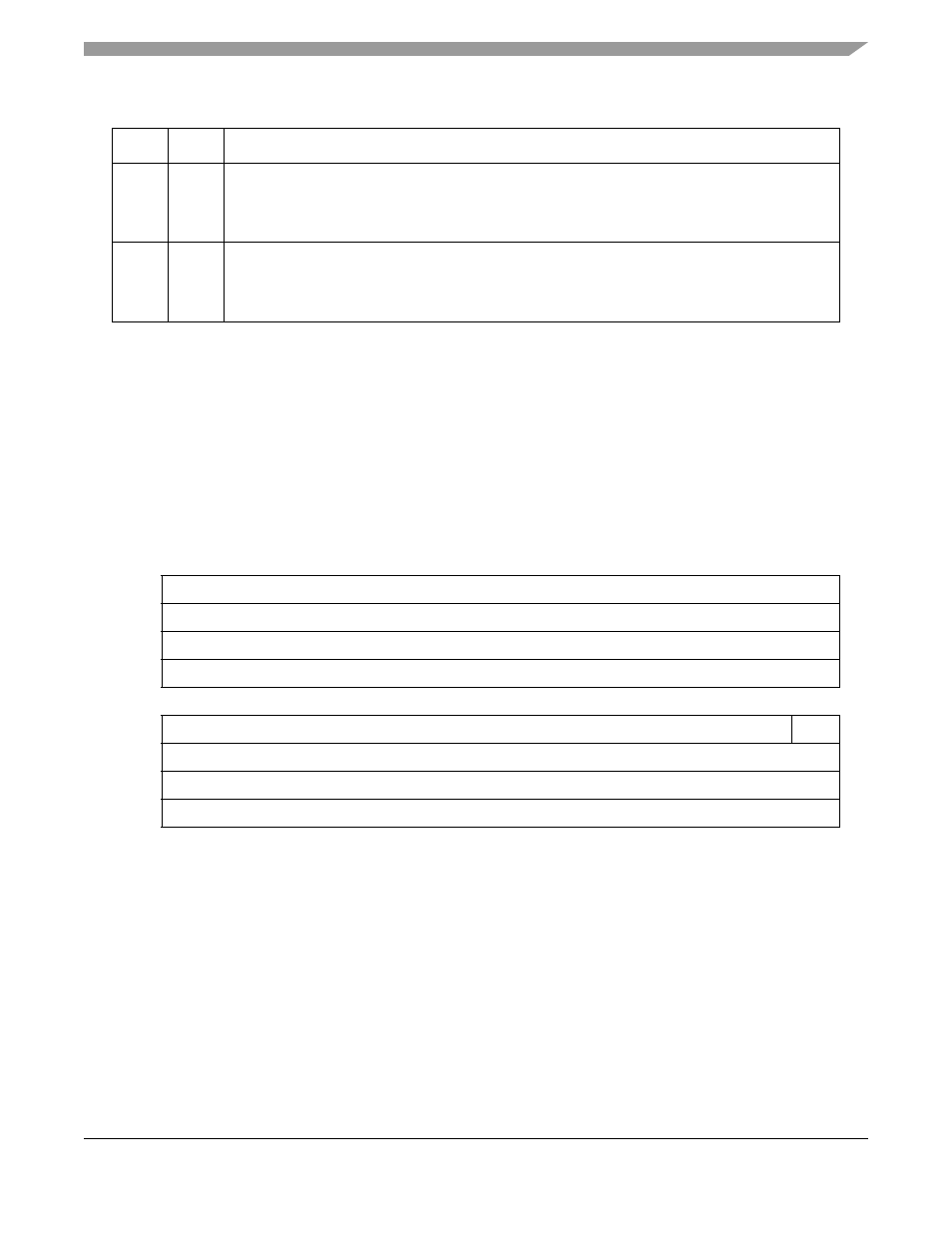

5.3

Reset Mode Register (RMR)

The reset mode register (RMR), shown in

, is memory-mapped into the SIU register map.

describes RMR fields.

30

ESRS

External soft reset status. When an external soft reset event is detected, ESRS is set and it remains

that way until software clears it. ESRS is cleared by writing a 1 to it (writing zero has no effect).

0 No external soft reset event has occurred

1 An external soft reset event has occurred

31

EHRS

External hard reset status. When an external hard reset event is detected, EHRS is set and it

remains set until software clears it. EHRS is cleared by writing a 1 (writing zero has no effect).

0 No external hard reset event has occurred

1 An external hard reset event has occurred

0

15

Field

—

R/W

R/W

Reset

0000_0000_0000_0000

Addr

16

30

31

Field

—

CSRE

R/W

R/W

Reset

0000_0000_0000_0000

Addr

0x10C96

Figure 5-3. Reset Mode Register (RMR)

Table 5-3. RSR Field Descriptions (continued)

Bits

Name

Function