Table 9-18. picmrx field descriptions, Pci inbound comparison mask registers (picmrx) -44, Picmrx field descriptions -44 – Freescale Semiconductor MPC8260 User Manual

Page 350: Table 9-18, Hown in, Figure 9-31, Table 9-18. describes picmr x

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-44

Freescale Semiconductor

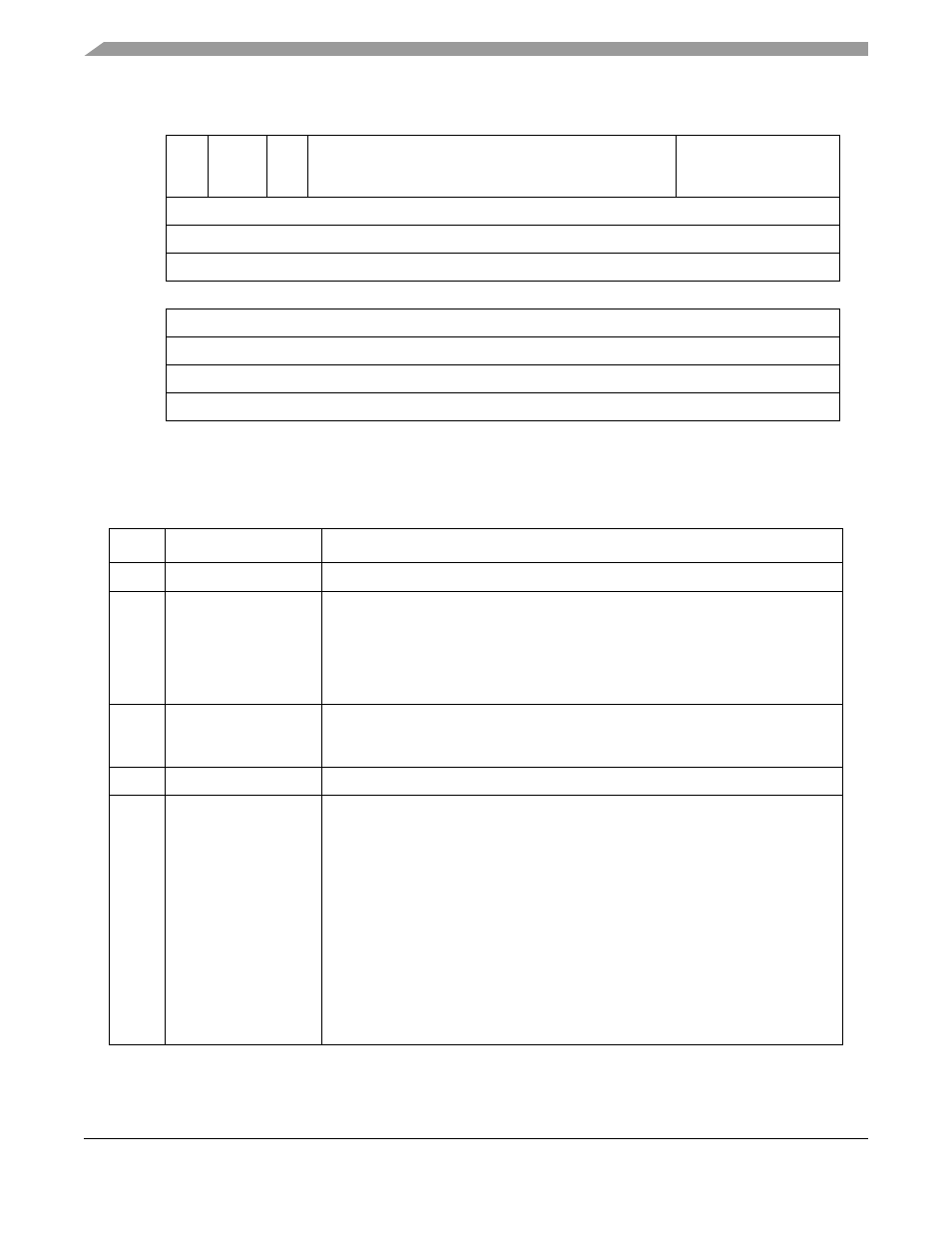

Figure 9-31. PCI Inbound Comparison Mask Registers (PICMR

x)

Table 9-18. describes PICMRx.

31

30

29

28

20

19

16

Field

EN

NO_

SNOOP_

EN

PRE

—

CM

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x108FA (PICMR0); 0x108E2 (PICMR1)

15

0

Field

CM

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x108F8 (PICMR0); 0x108E0 (PICMR1)

Table 9-18. PICMR

x Field Descriptions

Bits

Name

Description

31

Enable

Setting this bit enables address translation

30

NO_SNOOP_EN

Controls whether the PCI bridge generates snoop transactions on the 60x bus for

PCI-to-60x memory transactions which hit in this address translation window.

Disabling snooping is a performance enhancement for systems that do not need to

maintain coherency on system memory accesses by PCI.

0 Snooping is enabled.

1 Snooping is disabled.

29

Prefetchable

Indicates whether the address space is prefetchable so that streaming can occur.

0 not prefetchable

1 prefetchable

28–20

—

Reserved, should be cleared.

19–0

Comparison Mask

Indicates the size of the space to be translated. The value in the register represents

which of the most significant address bits to compare for a window match.

Non-contiguous comparison mask bits cause unpredictable behavior.

Examples:

PICMR = 0b0xxx_xxxx_xxxx_xxxx_xxxx_xxxx_xxxx_xxxx

Inbound window is disabled.

PICMR = 0b1xxx_xxxx_xxxx_1111_1111_1111_1111_1111

The mask is 20 bits (physical address bits 31-12) which corresponds to a 4Kbyte

window size. This is the smallest window size allowed.

PICMR = 0b1xxx_xxxx_xxxx_1111_1111_1111_0000_0000

The mask is 12 bits (physical address bits 31-20) which corresponds to a 1Mbyte

window size.