Freescale Semiconductor MPC8260 User Manual

Page 1314

Reference Manual (Rev 1) Errata

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

B-12

Freescale Semiconductor

33.4.1.1, 33-29

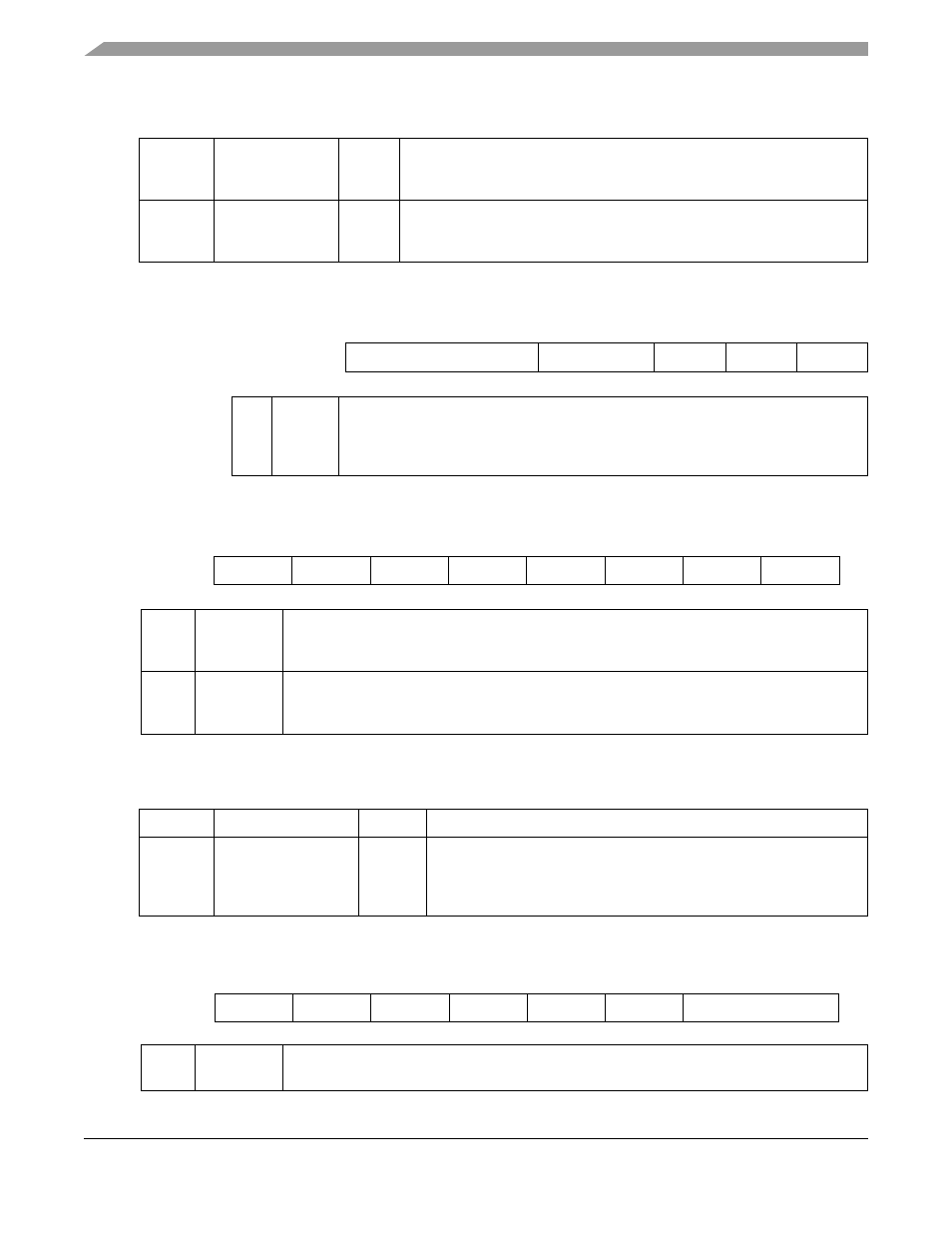

Add the following two rows to the bottom of Table 33-5:

33.4.4.1.1, 33-29

Add ISIE to Figure 33-14 and Table 33-6, as shown in the following:

33.4.4.1.2, 33-30

Add GTE and TRQS to Figure 33-15 and Table 33-7, as shown in the following:

33.4.4.2, 33-35

In Table 33-10 replace the descriptions of offsets 0x2C and 0x30 with the

following:

33.4.5.1.2, 33-40

Add LDC to Figure 33-22 and Table 33-17, as shown in the following:

0x0E

IASNCCTR

Byte

Required for optional TRL Service Latency enhancement only.

IMA APC Scheduled Number of Cells Counter - Number of cells passed to

the groups links upon request. Initialize to IASNC.

0x0F

IASNC

Byte

Required for optional TRL Service Latency enhancement only.

IMA APC Scheduled Number of Cells - reset for IASNCtr. Number of cells

passed to the groups links upon request. Recommended value is 1.

0

2

3

4

5

6

7

Field

—

TXSC

ISIE

CTC

ICPC

5

ISIE

Required for optional TRL Service Latency enhancement only.

IMA Scheduler Split Iterations Enable

0 - APC is not split, TRL completes round robin distribution of cells.

1 - APC split, both TRL and non-TRL requests distribute cells to the transmit queues.

0

1

2

3

4

5

6

7

Field

TSTF

TIMSTF

GTE

TRQS

ELX

—

ICH

ICPCA

2

GTE

Go to end flag - TRL has requested 2 times before round robin distribution has completed or

link will underrun and is still due a cell from round robin distribution. Microcode managed

parameter initialize to 0. Used for optional TRL Service Latency enhancement only.

3

TRQS

TRL Request - TRL has requested therefore 1 round robin distribution of cells and is yet to be

completed. Microcode managed parameter initialize to 0. Used for optional TRL Service

Latency enhancement only.

0x2C

—

Word

Reserved. Must be initialized to zero at group startups.

0x30

LINK_DCBO

Word

Link DCB overflow interrupt indication. Bit array identifying which links

have issued a link DCB overflow (DCBO) interrupt. This parameter

ensures that only one DCBO interrupt is generated per event.

Microcode managed parameter. Initialize to zero at group startup.

0

1

2

3

4

5

6

7

Field

LSTF

LIMSTF

LSTLFIP

LGSU

TQSU

LDC

—

5

LDC

Link Due Cell. Link is due cell from round robin distribution. Microcode managed parameter

initialize to 0. Used for optional TRL Service Latency enhancement only.