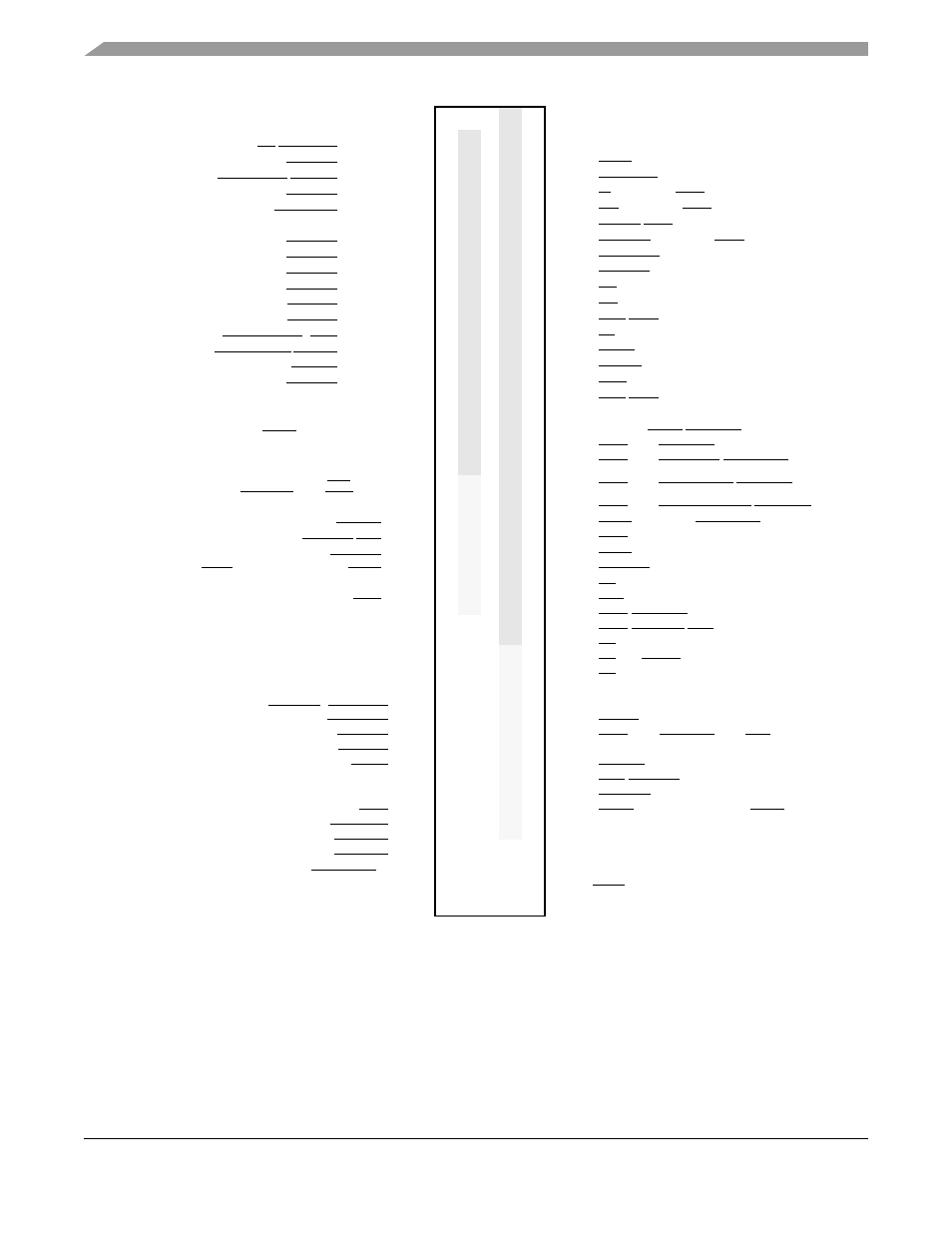

Figure 6-1. powerquicc ii external signals, 2 signal descriptions, Signal descriptions -2 – Freescale Semiconductor MPC8260 User Manual

Page 242: Powerquicc ii external signals -2

External Signals

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

6-2

Freescale Semiconductor

Figure 6-1. PowerQUICC II External Signals

6.2

Signal Descriptions

The PowerQUICC II system bus, shown in

, consists of all the signals that interface with the

external bus. Many of these pins perform different functions, depending on how the user assigns them.

VCCSYN/GNDSYN/VCCSYN1//VDDH/

VDD/VSS ⎯⎯⎯> 100

6

0

x

B

U

S

32

<⎯⎯> A[0–31]

PCI_PAR

1

/L_A14

1

MPC8250, MPC8265, and MPC8266 only.

<⎯⎯> 1

L

O

C

A

L

B

U

S

5

<⎯⎯> TT[0–4]

SMI/PCI_FRAME

1

/L_A15

<⎯⎯> 1

4

<⎯⎯> TSIZ[0–3]

PCI_TRDY

1

/L_A16

<⎯⎯> 1

1

<⎯⎯> TBST

CKSTOP_OUT/PCI_IRDY

1

/L_A17

<⎯⎯> 1

1

<⎯⎯> GBL/IRQ1

PCI_STOP

1

/L_A18

<⎯⎯> 1

1

<⎯⎯> CI/BADDR29/IRQ2

PCI_DEVSEL

1

/L_A19

<⎯⎯> 1

1

<⎯⎯> WT/BADDR30/IRQ3

PCI_IDSEL

1

/L_A20

<⎯⎯> 1

1

<⎯⎯⎯ L2_HIT/IRQ4

PCI_PERR

1

/L_A21

<⎯⎯> 1

1

<⎯⎯> CPU_BG/BADDR31/IRQ5

PCI_SERR/

1

L_A22

<⎯⎯> 1

1

⎯⎯⎯> CPU_DBG

PCI_REQ0

1

/L_A23

<⎯⎯> 1

1

⎯⎯⎯> CPU_BR

CPCI_HS_ES

1

/PCI_REQ1

1

/L_A24

<⎯⎯> 1

1

<⎯⎯> BR

PCI_GNT0

1

/L_A25

<⎯⎯> 1

1

<⎯⎯> BG

CPCI_HS_LED

1

/PCI_GNT1

1

/L_A26 <⎯⎯⎯ 1

1

<⎯⎯> ABB/IRQ2

CPCI_HS_ENUM

1

/GNT2

1

/L_A27

<⎯⎯> 1

1

<⎯⎯> TS

CORE_SRESET/PCI_RST

1

/L_A28

<⎯⎯> 1

1

<⎯⎯> AACK

PCI_INTA

1

/L_A29

<⎯⎯> 1

1

<⎯⎯> ARTRY

PCI_REQ2

1

/L_A30

<⎯⎯> 1

1

<⎯⎯> DBG

DLLOUT

1

/L_A31

<⎯⎯> 1

1

<⎯⎯> DBB/IRQ3

PCI_AD[31-0]

1

/LCL_D[0–31]

<⎯⎯> 32

64

<⎯⎯> D[0–63]

PCI_C/BE[3-0]

1

/LCL_DP[0–3]

<⎯⎯> 4

1

<⎯⎯> NC/DP0/RSRV/EXT_BR2

1

<⎯⎯> IRQ1/DP1/EXT_BG2

1

<⎯⎯> IRQ2/DP2/TLBISYNC/EXT_DBG2

PCI_CFG[3–0]

1

/LBS[0–3]/

LSDDQM[0–3]/LWE[0–3]

<⎯⎯⎯ 4

M

E

M

C

1

<⎯⎯> IRQ3/DP3/CKSTP_OUT/EXT_BR3

PCI_MODCK_H0

1

/LGPL0/LSDA10 <⎯⎯⎯

1

1

<⎯⎯> IRQ4/DP4/CORE_SRESET/EXT_BG3

PCI_MODCK_H1

1

/LGPL1/LSDWE <⎯⎯⎯

1

1

<⎯⎯> IRQ5/DP5/TBEN/EXT_DBG3

PCI_MODCK_H2

1

/LGPL2/LSDRAS/LOE

<⎯⎯⎯ 1

1

<⎯⎯> IRQ6/DP6/CSE0

PCI_MODCK_H3

1

/LGPL3/LSDCAS

<⎯⎯⎯ 1

1

<⎯⎯> IRQ7/DP7/CSE1

LPBS/LGPL4/LUPMWAIT/LGTA

<⎯⎯> 1

1

<⎯⎯> PSDVAL

PCI_MODCK

1

/LGPL5

<⎯⎯> 1

1

<⎯⎯> TA

LWR

<⎯⎯> 1

1

<⎯⎯> TEA

P

I

O

1

<⎯⎯> IRQ0/NMI_OUT

PA[0–31]

<⎯⎯> 32

1

<⎯⎯> IRQ7/INT_OUT/APE

PB[4–31]

<⎯⎯> 28

M

E

M

C

10

⎯⎯⎯> CS[0–9]

PC[0–31]

<⎯⎯> 32

1

<⎯⎯> CS[10]/BCTL1

PD[4–31]

<⎯⎯> 28

1

<⎯⎯> CS[11]/AP[0]

2

⎯⎯⎯> BADDR[27–28]

PCI_RST

1

/PORESET⎯⎯⎯> 1

R

S

T

C

L

K

1

⎯⎯⎯> ALE

RSTCONF

⎯⎯⎯> 1

1

⎯⎯⎯> BCTL0

HRESET

<⎯⎯> 1

8

⎯⎯⎯> PWE[0–7]/PSDDQM[0–7]/PBS[0–7]

SRESET

<⎯⎯> 1

1

⎯⎯⎯> PSDA10/PGPL0

QREQ

<⎯⎯⎯ 1

1

⎯⎯⎯> PSDWE/PGPL1

XFC

⎯⎯⎯> 1

1

⎯⎯⎯> POE/PSDRAS/PGPL2

CLKIN1

⎯⎯⎯> 1

1

⎯⎯⎯> PSDCAS/PGPL3

TRIS

⎯⎯⎯> 1

1

<⎯⎯> PGTA/PUPMWAIT/PGPL4/PPBS

BNKSEL[0]/TC[0]/AP[1]/MODCK1

<⎯⎯> 1

1

⎯⎯⎯> PSDAMUX/PGPL5

BNKSEL[1]/TC[1]/AP[2]/MODCK2

<⎯⎯> 1

J

T

A

G

1

<⎯⎯− TMS

BNKSEL[2]/TC[2]/AP[3]/MODCK3

<⎯⎯> 1

1

<⎯⎯⎯ TDI

PCI_MODE

2

2

MPC8250, MPC8265, and MPC8266 only. This is a spare pin on all other devices.

⎯⎯⎯> 1

1

<⎯⎯− TCK

CLKIN2

2

⎯⎯⎯> 1

1

<⎯⎯− TRST

NC

⎯⎯⎯> 2

1

−⎯⎯> TDO