2 configuration mechanism, 1 type 0 configuration translation, Configuration mechanism -60 – Freescale Semiconductor MCF5480 User Manual

Page 544

MCF548x Reference Manual, Rev. 3

19-60

Freescale Semiconductor

19.4.4.2

Configuration Mechanism

In order to support both Type 0 and Type 1 configuration transactions, the MCF548x provides the 32 bit

configuration address register (PCICAR). The register specifies the target PCI bus, device, function, and

configuration register to be accessed. A read or a write to the MCF548x window defined as PCI I/O space,

in PCIIWCR, causes the host bridge to translate the access into a PCI configuration cycle if the enable bit

in the configuration address register is set and the device number does not equal 0b1_1111. For space to

be defined as I/O space, the accessed space (one of the initiator windows) must be programmed as I/O, not

memory. See

Section 19.3.2.8, “Initiator Window Configuration Register (PCIIWCR)

The format of the configuration address register is shown in

Section 19.3.2.11, “Configuration Address

”.When the MCF548x detects an access to an I/O window, it checks the enable flag and

the device number in the configuration address register. If the enable bit is set, and the device number is

not 0b1_1111, the MCF548x performs a configuration cycle translation function and runs a configuration

read or configuration write transaction on the PCI bus. The device number 0b1_1111 is used for

performing interrupt acknowledge and special cycle transactions. See

and

Section 19.4.4.4, “Special Cycle Transactions,”

for more information. If

the bus number corresponds to the local PCI bus (bus number = 0x00), a Type 0 configuration cycle

transaction is performed. If the bus number indicates a remote PCI bus, the MCF548x performs a Type 1

configuration cycle translation. If the enable bit is not set, the access to the configuration window is passed

through to the PCI bus as an I/O transfer (window translation applies).

Note that the PCI data byte enables (PCICXBE[3:0]) are determined by the size access to the window.

19.4.4.2.1

Type 0 Configuration Translation

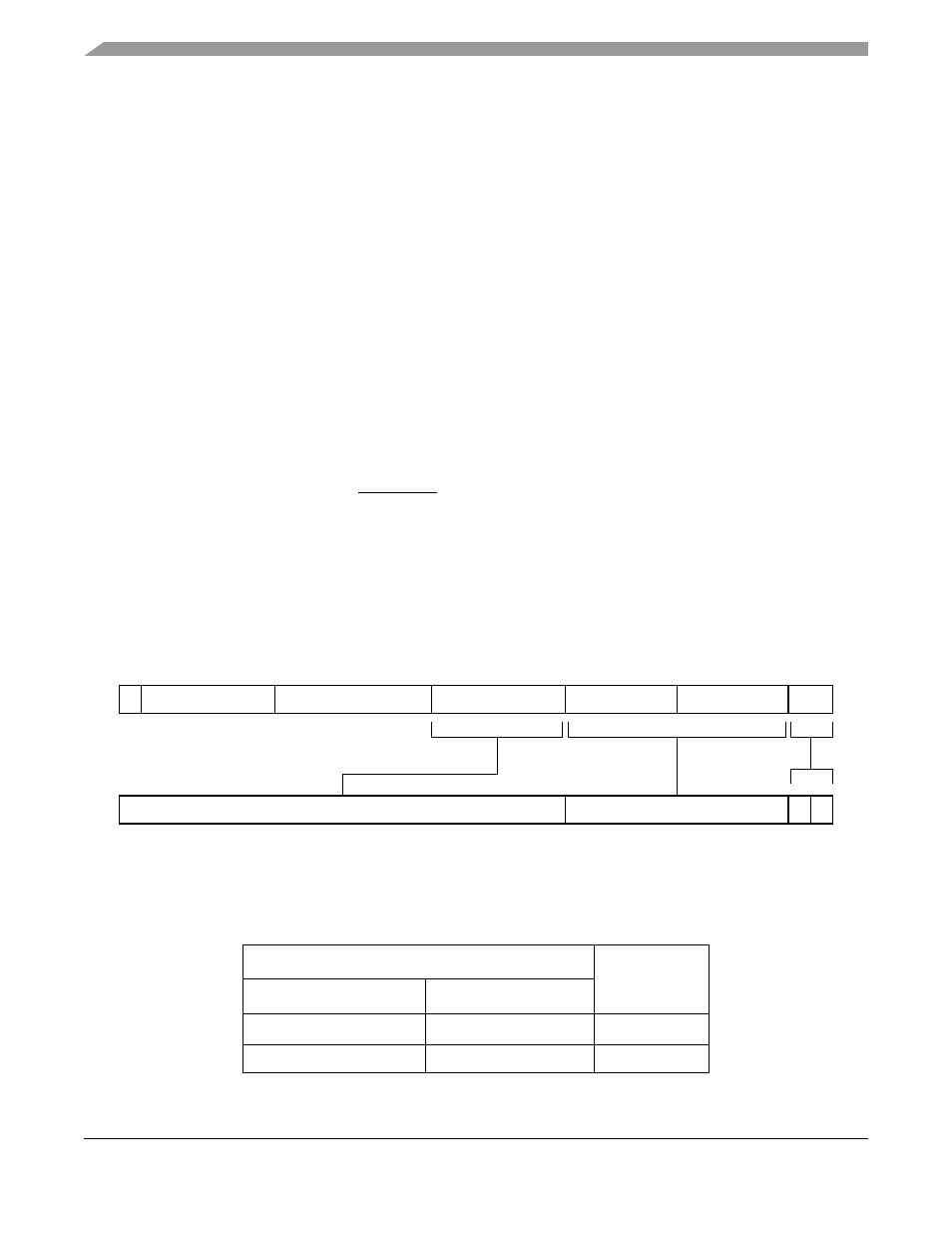

shows the Type 0 translation function performed on the contents of the configuration address

register to the AD[31:0] signals on the PCI bus during the address phase of the configuration cycle (this

only applies when the enable bit in the configuration address register is set).

Figure 19-53. Type 0 Configuration Translation

For Type 0 configuration cycles, the MCF548x translates the device number field of the configuration

address register into a unique IDSEL line shown in

. It allows for 21 different devices.

Table 19-50. Type 0 Configuration Device Number to IDSEL Translation

Device Number

IDSEL

Binary

Decimal

0b0_0000-0b0_1001

1

0–9

-

0b0_1010

10

AD31

31 30

24 23

16 15

11 10

8

7

2

1

0

E

Reserved

Bus Number

Device Number

Function Number

Dword

Rsvd

Contents of Configuration Address Register:

31

11 10

2

1

0

IDSEL (Only One Signal High)

Function Number/Dword

0

0

PCIAD[31:0] Signals During Address Phase: