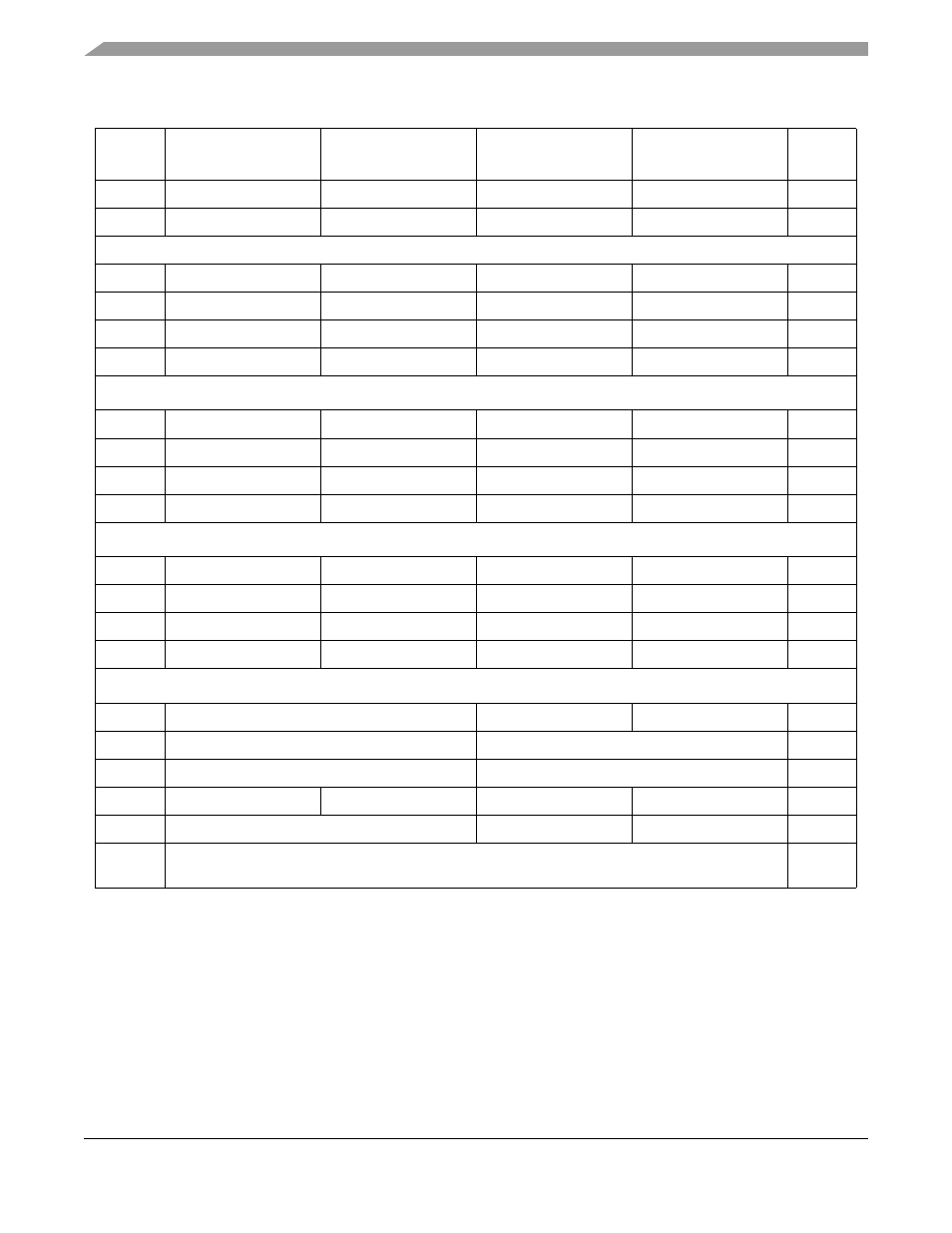

2 register descriptions, 1 port x output data registers (podr_x), Register descriptions -8 – Freescale Semiconductor MCF5480 User Manual

Page 380: Port, 1 port x output data registers (podr_ x )

MCF548x Reference Manual, Rev. 3

15-8

Freescale Semiconductor

15.3.2

Register Descriptions

15.3.2.1

Port x Output Data Registers (PODR_x)

The PODR registers store the data to be driven on the corresponding port x pins when the pins are

configured for general purpose output.

0xA08

PODR_FECI2C

PODR_PCIBG

PODR_PCIBR

Reserved

3

S/U

0xA0C

PODR_PSC3PSC2

PODR_PSC1PSC0

PODR_DSPI

Reserved

3

S/U

Port Data Direction Registers

0xA10

PDDR_FBCTL

PDDR_FBCS

PDDR_DMA

Reserved

2

S/U

0xA14

PDDR_FEC0H

PDDR_FEC0L

PDDR_FEC1H

PDDR_FEC1L

S/U

0xA18

PDDR_FECI2C

PDDR_PCIBG

PDDR_PCIBR

Reserved

3

S/U

0xA1C

PDDR_PSC3PSC2

PDDR_PSC1PSC0

PDDR_DSPI

Reserved

3

S/U

Port Pin Data/Set Data Registers

0xA20

PPDSDR_FBCTL

PPDSDR_FBCS

PPDSDR_DMA

Reserved

3

S/U

0xA24

PPDSDR_FEC0H

PPDSDR_FEC0L

PPDSDR_FEC1H

PPDSDR_FEC1L

S/U

0xA28

PPDSDR_FECI2C

PPDSDR_PCIBG

PPDSDR_PCIBR

Reserved

3

S/U

0xA2C

PPDSDR_PSC3PSC2

PPDSDR_PSC1PSC0

PPDSDR_DSPI

Reserved

3

S/U

Port Clear Output Data Registers

0xA30

PCLRR_FBCTL

PCLRR_FBCS

PCLRR_DMA

Reserved

3

S/U

0xA34

PCLRR_FEC0H

PCLRR_FEC0L

PCLRR_FEC1H

PCLRR_FEC1L

S/U

0xA38

PCLRR_FECI2C

PCLRR_PCIBG

PCLRR_PCIBR

Reserved

3

S/U

0xA3C

PCLRR_PSC3PSC2

PCLRR_PSC1PSC0

PCLRR_DSPI

Reserved

3

S/U

Pin Assignment Registers

0xA40

PAR_FBCTL

PAR_FBCS

PAR_DMA

S/U

0xA44

PAR_FECI2CIRQ

Reserved

3

S/U

0xA48

PAR_PCIBG

PAR_PCIBR

S/U

0xA4C

PAR_PSC3

PAR_PSC2

PAR_PSC1

PAR_PSC0

S/U

0xA50

PAR_DSPI

PAR_TIMER

Reserved

3

S/U

0xA54–

0xA7F

Reserved

3

1

S/U = supervisor or user mode access.

2

Reads to reserved locations return 0s. Writes have no effect.

Table 15-3. MCF548x GPIO Module Memory Map (Continued)

MBAR

Offset

31–24

23–16

15–8

7–0

Access

1