8 exception processing overview, Exception processing overview -36 – Freescale Semiconductor MCF5480 User Manual

Page 140

MCF548x Reference Manual, Rev. 3

3-36

Freescale Semiconductor

3.8

Exception Processing Overview

Exception processing for ColdFire processors is streamlined for performance. Differences from previous

ColdFire Family processors include the following:

•

An instruction restart model for translation (TLB miss) and access faults. This new functionality

extends the existing ColdFire access error fault vector and exception stack frames.

•

Use of separate system stack pointers for user and supervisor modes.

Previous ColdFire processors use an instruction restart exception model but require additional software

support to recover from certain access errors.

Exception processing can be defined as the time from the detection of the fault condition until the fetch of

the first handler instruction has been initiated. It consists of the following four major steps:

1. The processor makes an internal copy of the status register (SR) and then enters supervisor mode

by setting SR[S] and disabling trace mode by clearing SR[T]. The occurrence of an interrupt

exception also clears SR[M] and sets the interrupt priority mask, SR[I] to the level of the current

interrupt request.

2. The processor determines the exception vector number. For all faults except interrupts, the

processor bases this calculation on exception type. For interrupts, the processor performs an

interrupt acknowledge (IACK) bus cycle to obtain the vector number from peripheral. The IACK

cycle is mapped to a special acknowledge address space with the interrupt level encoded in the

address.

The processor saves the current context by creating an exception stack frame on the system stack.

As a result, the exception stack frame is created at a 0-modulo-4 address on top of the system stack

pointed to by the supervisor stack pointer (SSP). As shown in

, the CF4e processor uses

the same fixed-length stack frame as previous ColdFire Versions with additional fault status (FS)

encodings to support the MMU. In some exception types, the program counter (PC) in the

exception stack frame contains the address of the faulting instruction (fault); in others the PC

contains the next instruction to be executed (next). (Note that previous ColdFire processors support

a single stack pointer in the A7 address register.)

fsave

—

—

7(0/3)

—

—

7(0/3)

—

fsqrt

56(0/0)

56(0/0)

56(1/0)

56(1/0)

56(1/0)

56(1/0)

56(1/0)

fsub

4(0/0)

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

ftst

1(0/0)

1(0/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1

Add 1(1/0) for an external read operand of double-precision format for all instructions except FMOVEM, and

1(0/1) for FMOVE FPy,

2

If the external operand is an integer format (byte, word, or longword), there is a 4-cycle conversion time that

must be added to the basic execution time.

3

For FMOVEM, n refers to the number of registers being moved.

4

If any exceptions are enabled, the execution time for FMOVE FPy,

exception is enabled, the execution time for FBcc increases by one cycle.

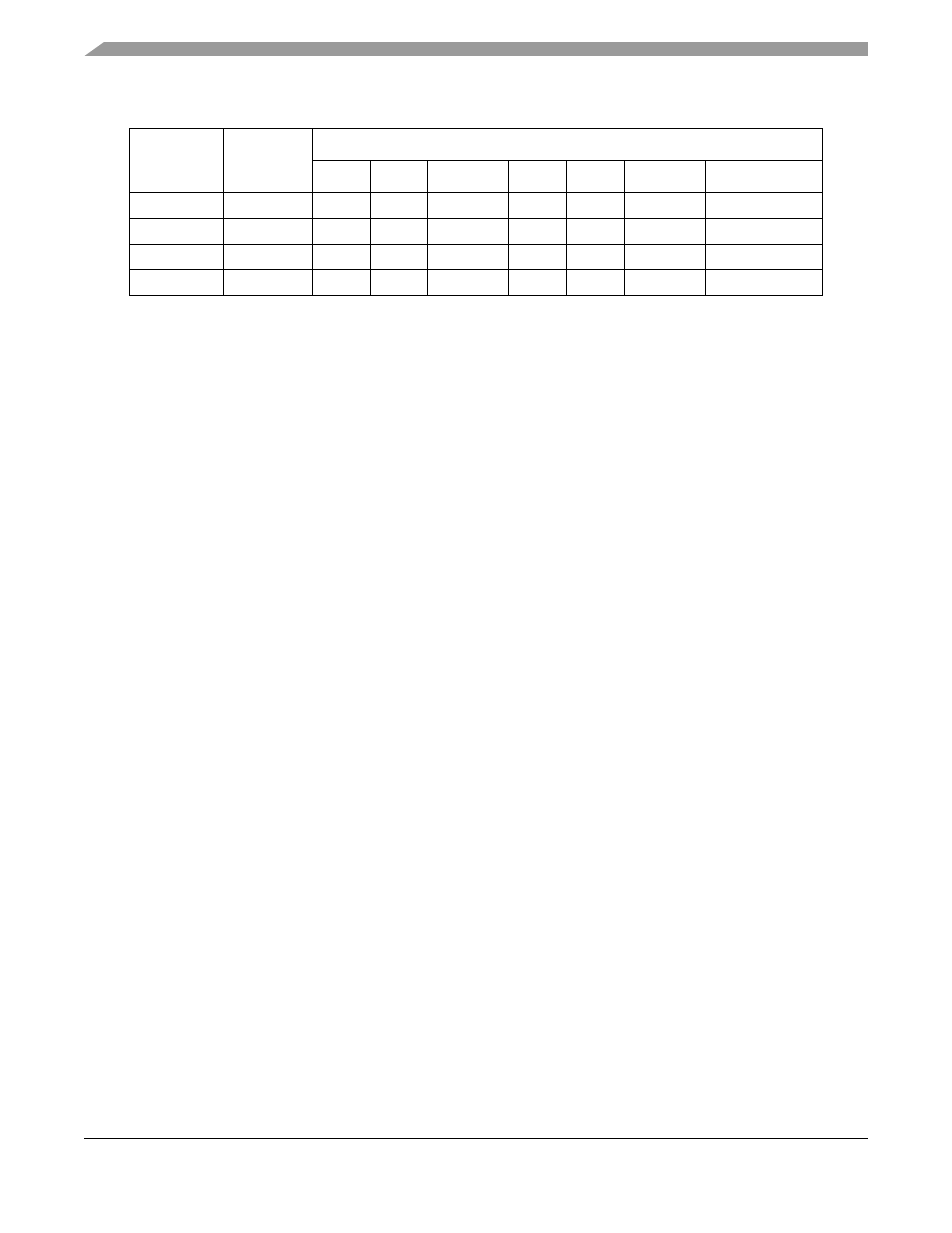

Table 3-20. FPU Instruction Execution Times

1,

2

Opcode

Format

Effective Address

FPn

Dn

(An)

(An)+

–(An)

(d

16

,An)

(d

16

,PC)