10 cache register definition, 1 cache control register (cacr), Cache register definition -19 – Freescale Semiconductor MCF5480 User Manual

Page 239: Cache control register (cacr) -19, Write-protect fields. see, Section 7.10.1, “cache control register (cacr)

Cache Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

7-19

7.10

Cache Register Definition

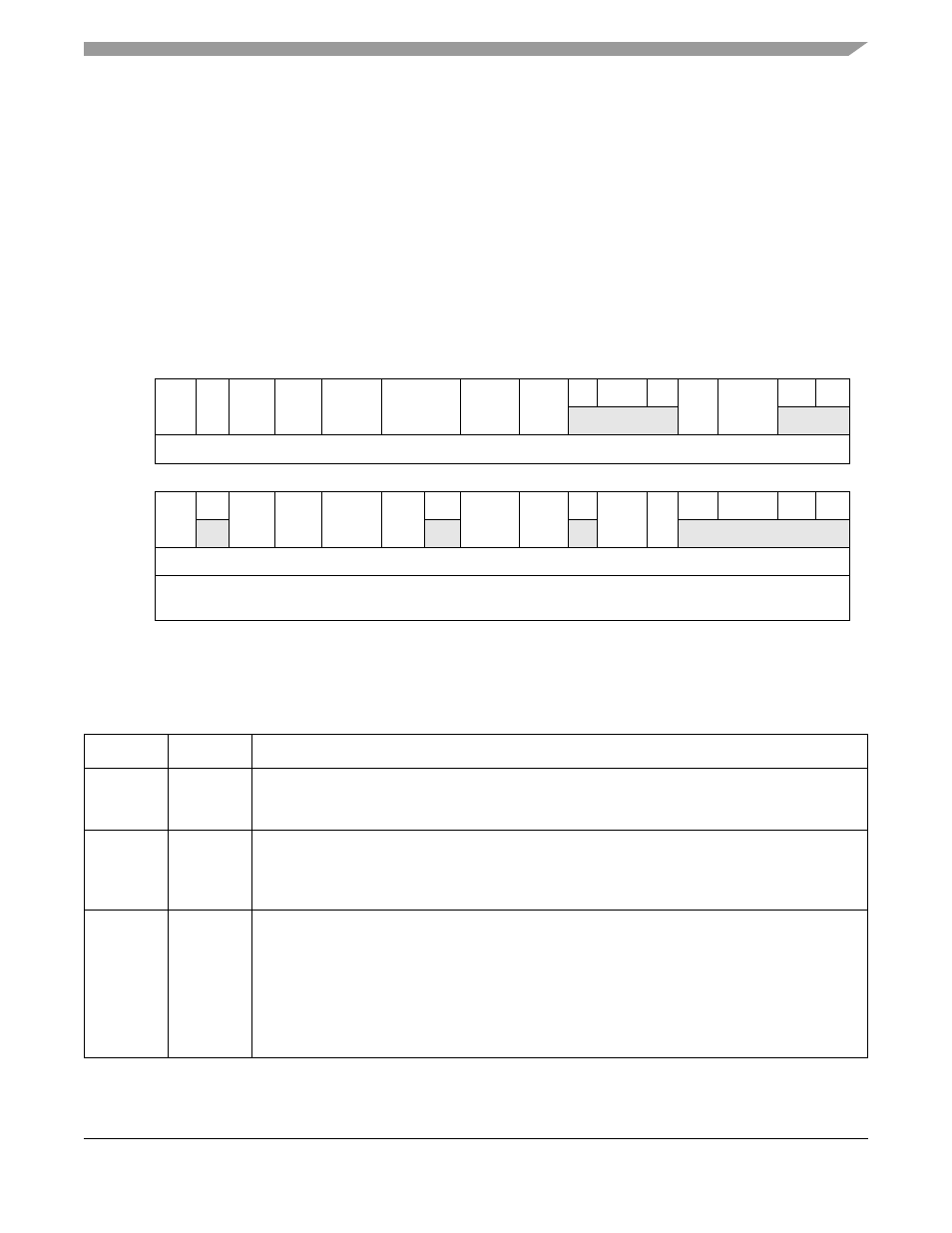

This section describes the MCF548x implementation of the Version 4e cache registers.

7.10.1

Cache Control Register (CACR)

contains bits for configuring the cache. It can be written by the MOVEC register

instruction and can be read or written from the debug facility. A hardware reset clears CACR, which

disables the cache; however, reset does not affect the tags, state information, or data in the cache.

NOTE

CACR is read/write by the debug module.

describes CACR fields. Note that some implementations may include fields not defined here;

consult the part-specific documentation.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R DEC DW DESB DDPI DHLCK

DDCM

DCINVA DDSP

0

0

0

BEC BCINVA

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R IEC

0

DNFB

IDPI

IHLCK IDCM

0

ICINVA

IDSP

0

EUSP DF

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

0x002

Figure 7-8. Cache Control Register (CACR)

Table 7-4. CACR Field Descriptions

Bits

Name

Description

31

DEC

Enable data cache.

0 Cache disabled. The data cache is not operational, but data and tags are preserved.

1 Cache enabled.

30

DW

Data default write-protect. For normal operations that do not hit in the RAMBARs or ACRs, this field

defines write-protection. See

.”

0 Not write protected.

1 Write protected. Write operations cause an access error exception.

29

DESB

Enable data store buffer. Affects the precision of transfers.

0 Imprecise-mode, write-through or cache-inhibited writes bypass the store buffer and generate

bus cycles directly.

Section 7.9.4.2.1, “Push and Store Buffers

,” describes the associated

performance penalty.

1 The four-entry FIFO store buffer is enabled; to maximize performance, this buffer defers pending

imprecise-mode, write-through or cache-inhibited writes.

Precise-mode, cache-inhibited accesses always bypass the store buffer. Precise and imprecise

modes are described in

Section 7.9.1.2, “Cache-Inhibited Accesses

.”