Endpoint, Table 29-29/29-30 – Freescale Semiconductor MCF5480 User Manual

Page 904

MCF548x Reference Manual, Rev. 3

29-30

Freescale Semiconductor

29.2.4.4

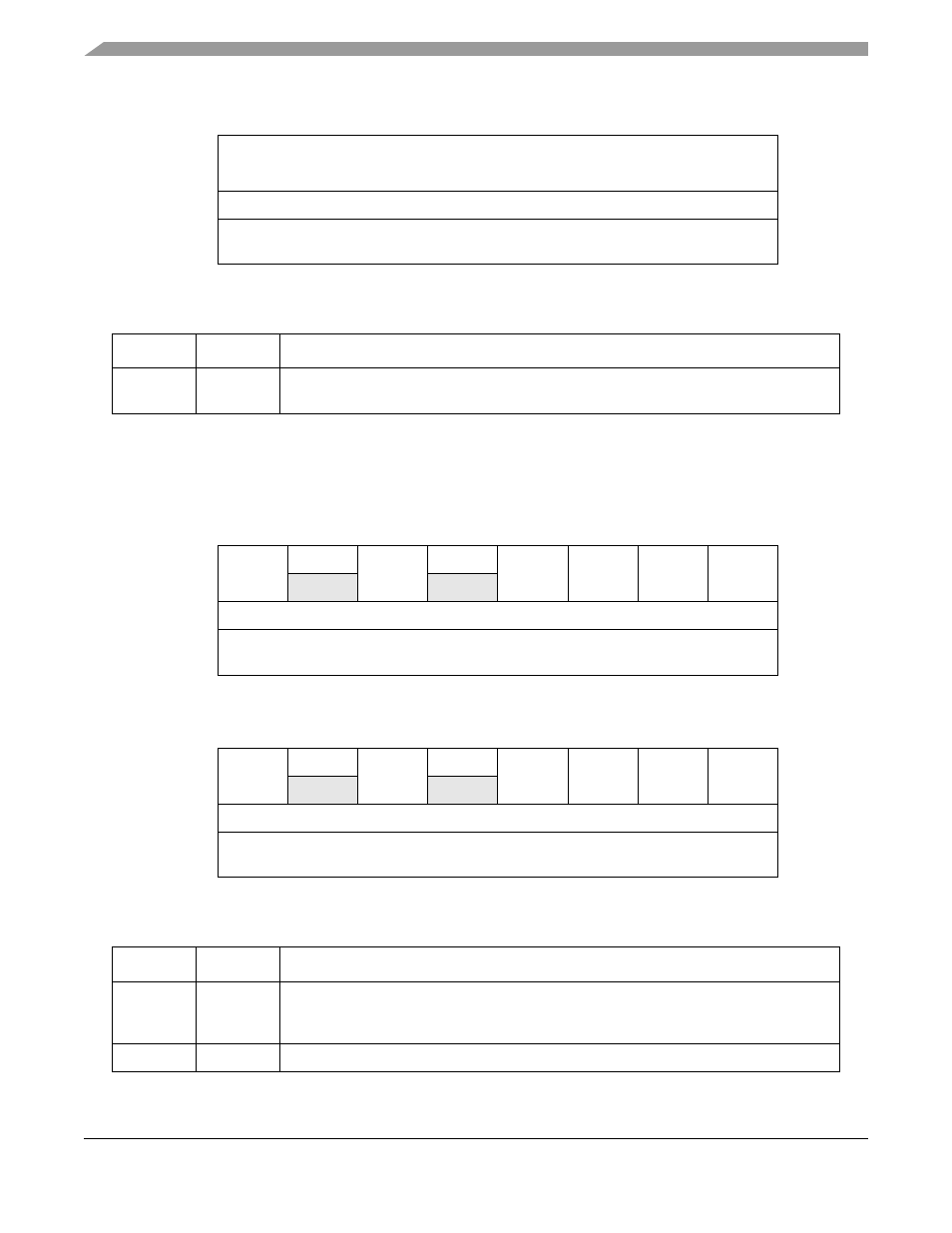

Endpoint n Status Register (EP0SR, EPnOUTSR, EPnINSR)

The endpoint status register contains the status for the specified endpoint. The ACTIVE bit of this register

must be set before doing any transaction on this endpoint.

7

6

5

4

3

2

1

0

R

IFNUM

W

Reset

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0xB14C(EP1NIFNUM); 0xB17C(EP2NIFNUM); 0xB1AC(EP3INIFR);

0xB1DC(EP4INIFR); 0xB20C(EP5INIFR); 0xB23C(EP6INIFR)

Figure 29-31. Endpoint n Interface Number Register IN (EPnINIFR)

Table 29-28. EPnOUTIFR and EPnINIFR Field Descriptions

Bits

Name

Description

7–0

IFNUM

Interface number. This register contains the interface number associated with the specified

endpoint. The interface number may range from 0x00 through 0xFF.

7

6

5

4

3

2

1

0

R

INT

0

TXZERO

0

CCOMP

PSTALL

ACTIVE

HALT

W

Reset

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0xB105(EP0OUTSR); 0xB135(EP1OUTSR); 0xB165(EP2OUTSR);

0xB195(EP3OUTSR); 0xB1C5(EP4OUTSR); 0xB1F5(EP5OUTSR); 0xB225(EP6OUTSR)

Figure 29-32. Endpoint n Status Register OUT (EPnOUTSR)

7

6

5

4

3

2

1

0

R

INT

0

TXZERO

0

CCOMP

PSTALL

ACTIVE

HALT

W

Reset

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0xB14D(EP1INSR); 0xB17D(EP2INSR); 0xB1AD(EP3INSR);

0xB1DD(EP4INSR); 0xB20D(EP5INSR); 0xB23D(EP6INSR)

Figure 29-33. Endpoint n Status Register IN (EPnINSR)

Table 29-29. EPnOUTSR and EPnINSR Field Descriptions

Bits

Name

Description

7

INT

Interrupt. Relevant only for interrupt IN endpoints. Write 0 to clear.

0 No interrupt pending on this endpoint (default).

1 Interrupt pending on this endpoint.

6

—

Reserved, should be cleared.