7 fir mode, Fir mode -54 – Freescale Semiconductor MCF5480 User Manual

Page 816

MCF548x Reference Manual, Rev. 3

26-54

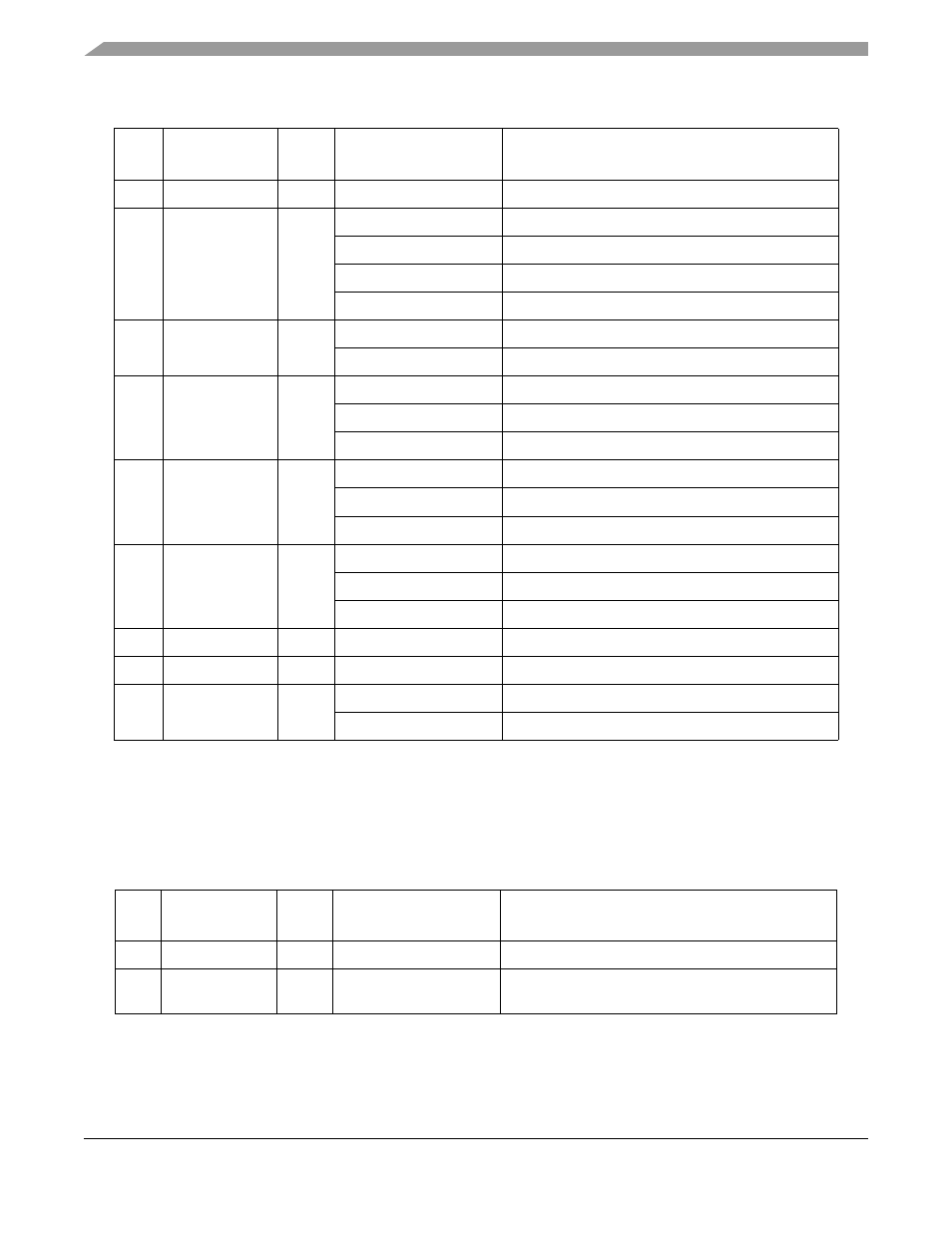

Freescale Semiconductor

26.7.2.7

FIR Mode

Applying the clock to the PSCBCLK input and programming the control registers are required to initialize

in FIR mode. Here is a sample sequence when the input frequency of PSCBCLK is 64 MHz. Steps 3 to 11

are the same as in MIR mode.

4

PSCMR1

73

RxIRQ=1

receiver interrupt is from FU (over threshold)

5

PSCIMR

0380

IPC=0

Disable input port change interrupt

RxRDY or FU=1

Enable receiver interrupt/request

TxRDY=1

Enable transmitter interrupt/request

DEOF=1

Enable DEOF interrupt/request

6

PSCIRCR1

02

FD=0

Receiver is disabled while transmitting

SIPEN=1

Send SIP after every frame

7

PSCIRCR2

00

SIPREQ=0

SIP is not requested to send now

ABORT=0

Not send abort sequence now

NXTEOF=0

Next write is not EOF

8

PSCRFCR

0F

WRITE TAG = 00

Not EOF

FRMEN=1

Enable frame mode

GR[2:0]=100

Granularity is 4 byte

9

PSCTFCR

0F

WRITE TAG = 00

Not EOF

FRMEN=1

Enable frame mode

GR[2:0]=100

Granularity is 16 byte

10

PSCRFAR

00F0

ALARM[8:0]=0F0

Request is asserted if # of data >= 240

11

PSCTFAR

00F0

ALARM[8:0]=0F0

Request is asserted if # of empty >= 240

12

PSCCR

04

TC=01

Enable transmitter

RC=00

receiver remains at disabled state.

Table 26-46. A Sample Initialization Sequence for FIR Mode

Step

No.

Register

Value

Details

Meaning

1

PSCSICR

06

SIM[2:0]=110

FIR mode

2

PSCIRFFD

0F

F_FDIV[3:0]=0111

Frequency divide ratio is 8.

So f(PSCBCLK) should be 64 MHz.

Table 26-45. A Sample Initialization Sequence for MIR Mode (Continued)

Step

No.

Register

Value

Details

Meaning