Appendix a mcf548x memory map, Mcf548x memory map – Freescale Semiconductor MCF5480 User Manual

Page 1011

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

A-1

Appendix A

MCF548x Memory Map

lists an overview of the memory map for the on-chip modules.

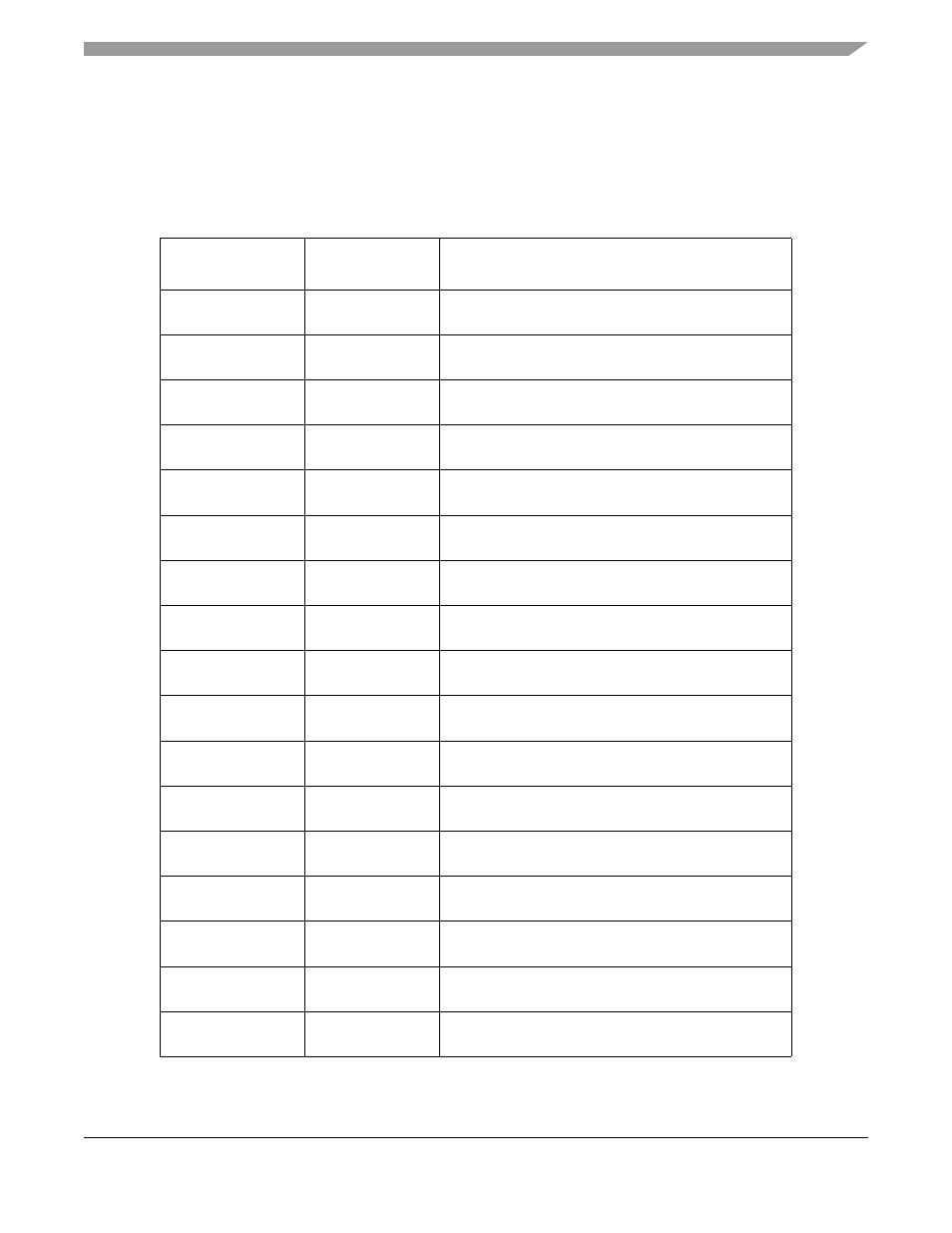

Table A-1. MCF548x Module Memory Map Overview

Address

Name

(abbreviation)

Description

MBAR + 0x0000 –

0x00FF

SIU

SIU overview registers

MBAR + 0x0100 –

0x01FF

SDRAMC

SDRAM Controller registers

MBAR + 0x0200 –

0x02FF

XARB

XLB Arbiter registers

MBAR + 0x0300 –

0x04FF

Reserved

—

MBAR + 0x0500 –

0x05FF

FBIC

FlexBus Interface Controller registers

MBAR + 0x0600 –

0x06FF

Reserved

—

MBAR + 0x0700 –

0x07FF

INTC

Interrupt Controller registers

MBAR + 0x0800 –

0x08FF

GPT

General Purpose Timer registers

MBAR + 0x0900 –

0x09FF

SLT

Slice Timer registers

MBAR + 0x0A00 –

0x0AFF

GPIO

GPIO registers and Pin configuration (from reindeer

project)

MBAR + 0x0B00 –

0x0BFF

PCI

PCI registers

MBAR + 0x0C00 –

0x0CFF

PCI ARB

PCI Arbiter registers

MBAR + 0x0D00 –

0x0DFF

EXTDMA

External DMA request registers

MBAR + 0x0E00 –

0x0EFF

Reserved

—

MBAR + 0x0F00 –

0x0FFF

EPORT

Edge Port registers

MBAR + 0x1000 –

0x7EFF

Reserved

—

MBAR + 0x7F00 –

0x7FFF

CTM

Comm Timer registers