1 sdram drive strength register (sdramds), Sdram drive strength register (sdramds) -17 – Freescale Semiconductor MCF5480 User Manual

Page 465

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

18-17

18.7.1

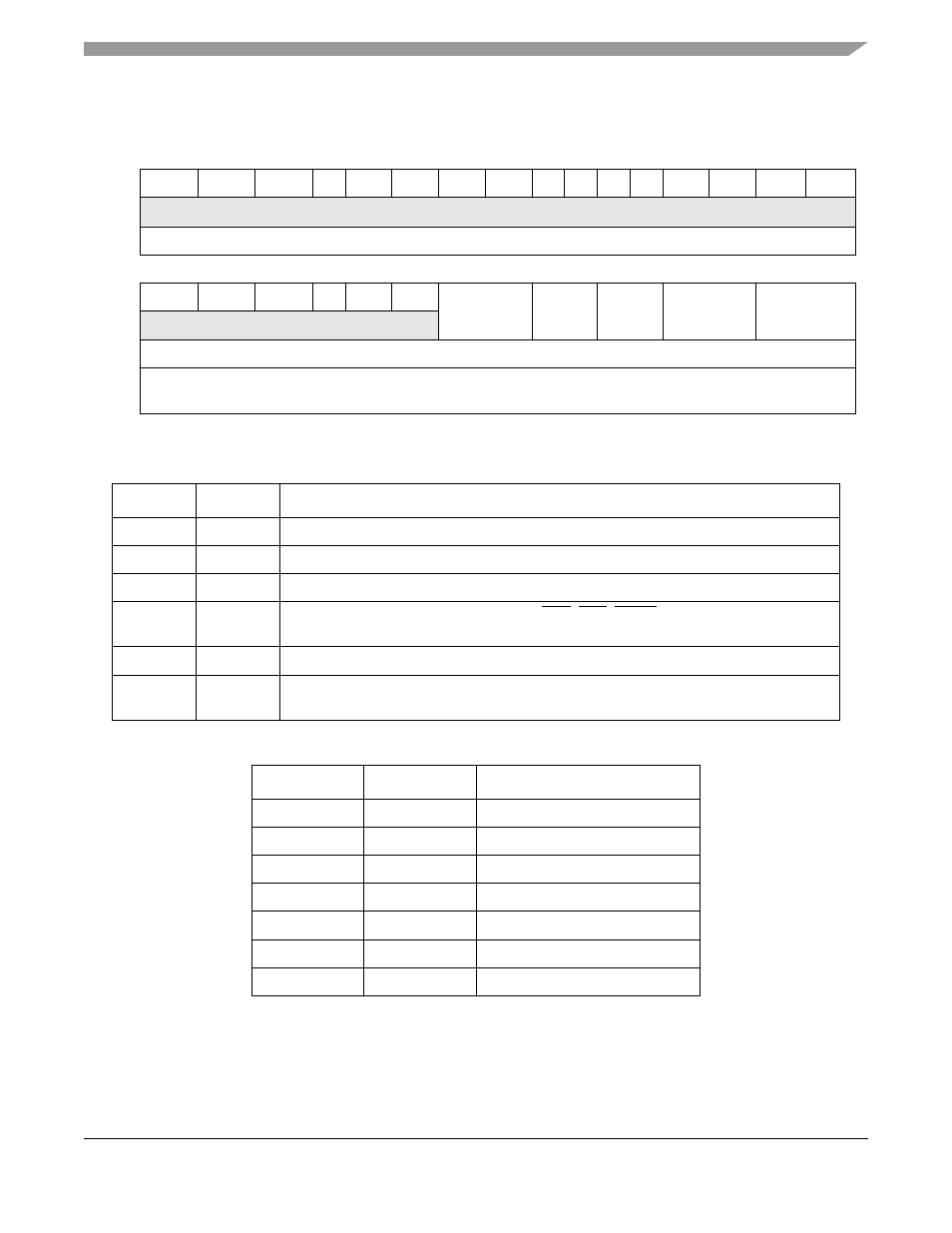

SDRAM Drive Strength Register (SDRAMDS)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

SB_E

SB_C

SB_A

SB_S

SB_D

W

Reset

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

Reg

Addr

MBAR + 0x04

Figure 18-8. SDRAM Drive Strength Register (SDRAMDS)

Table 18-7. SDRAMDS Field Descriptions

Bits

Name

Description

31–10

—

Reserved. Should be cleared

9–8

SB_E

Controls the drive strength of SDCKE. See

for encodings.

7–6

SB_C

Controls the drive strength of SDRAM clocks. See

for encodings.

5–4

SB_A

Controls the drive strength of SDCS[3:0], RAS, CAS, SDWE, SDADDR[12:0], and

SDBA[1:0]. See

for encodings.

3–2

SB_S

Controls the drive strength of SDRDQS. See

for encodings.

1–0

SB_D

Controls the drive strength of SDDATA[31:0], SDDM[3:0], and SDQS[3:0]. See

for encodings.

Table 18-8. SDRAM Drive Strength Bit Encodings

SB_x[1:0]

SD_VDD

1

1

3.3V is for SDR mode, 2.5V is for DDR mode

Drive

10

3.3

8mA; SSTL_3 Class I

01

3.3

16mA; SSTL_3 Class II

00

3.3

24mA; SSTL_3

10

2.5

7.6mA; SSTL_2 Class I

01

2.5

13mA

00

2.5

15mA; SSTL_2 Class II

11

X

No Drive;Hi-Z