16 infrared control register 1 (pscircr1n), 17 infrared control register 2 (pscircr2n), Infrared control register 1 (pscircr1n) -24 – Freescale Semiconductor MCF5480 User Manual

Page 786: Infrared control register 2 (pscircr2n) -24, 16 infrared control register 1 (pscircr1 n ), 17 infrared control register 2 (pscircr2 n )

MCF548x Reference Manual, Rev. 3

26-24

Freescale Semiconductor

26.3.3.16 Infrared Control Register 1 (PSCIRCR1n)

This register controls the configuration in IrDA mode.

26.3.3.17 Infrared Control Register 2 (PSCIRCR2n)

This register sets some requests to the transmitter or the TxFIFO.

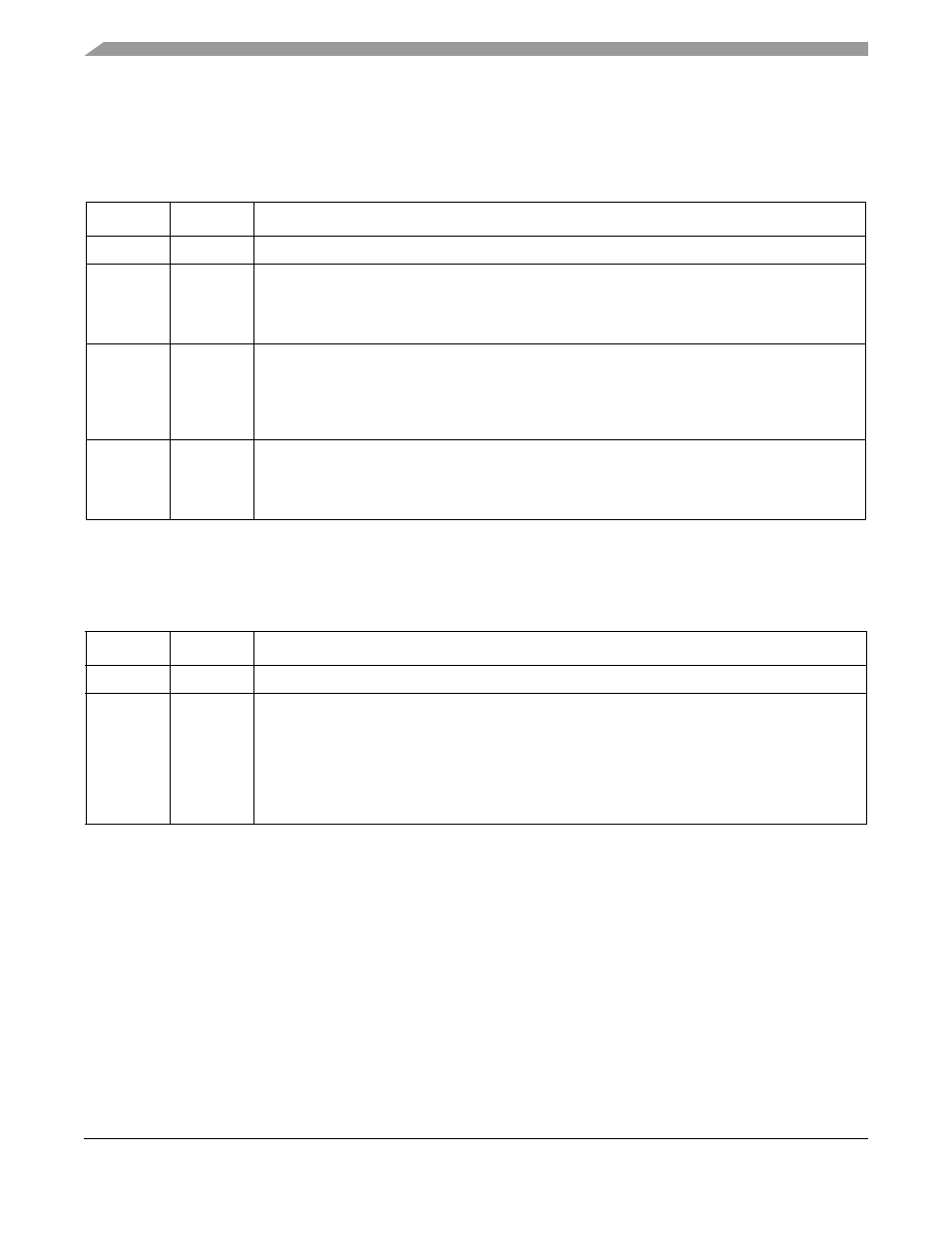

Table 26-22. PSCIRCR1n Field Descriptions

Bits

Name

Description

7–4

—

Reserved, should be cleared.

2

FD

In MIR, FIR, SIR, and modem modes, this bit signifies full duplex enable.

0 The receiver in IrDA mode is disabled while the transmitter is busy.

1 The receiver in IrDA mode is not disabled while the transmitter is busy. This bit should not be set

in usual operations. In loop back channel mode, CM=10, this bit is automatically set.

1

SIPEN

In SIR mode this bit is reserved.

In MIR, FIR, and modem mode, this bit signifies sends SIP enable after every frame.

0 SIP is sent only when the SIPREQ bit in the PSCIRCR2 becomes high.

1 The transmitter always send 1.6 us SIP after the STO flag in order to inform slow speed devices

that higher speed device is connecting.

0

SPUL

In MIR, FIR, and modem modes this bit is reserved.

In SIR mode, this bit signifies SIR pulse width.

0 SIR pulse width is 3/16 of the bit duration.

1 SIR pulse width is 1.6

µs

Table 26-23. PSCIRCR2n Field Descriptions

Bits

Name

Descriptions

7–3

—

Reserved, should be cleared.

2

SIPREQ

In all other modes besides MIR and FIR, this bit is reserved.

In MIR and FIR mode, this bit signifies request to send SIP.

0 No operation

1 If the transmitter becomes idle state, the transmitter starts to send one SIP pulse. This bit keeps

high until the transmitter finishes sending a SIP and becomes low automatically when the

transmitter finishes sending a SIP.