3 reset status register (rsr), 4 jtag device identification number (jtagid), Reset status register (rsr) -5 – Freescale Semiconductor MCF5480 User Manual

Page 321: Jtag device identification number (jtagid) -5

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

9-5

9.3.1.3

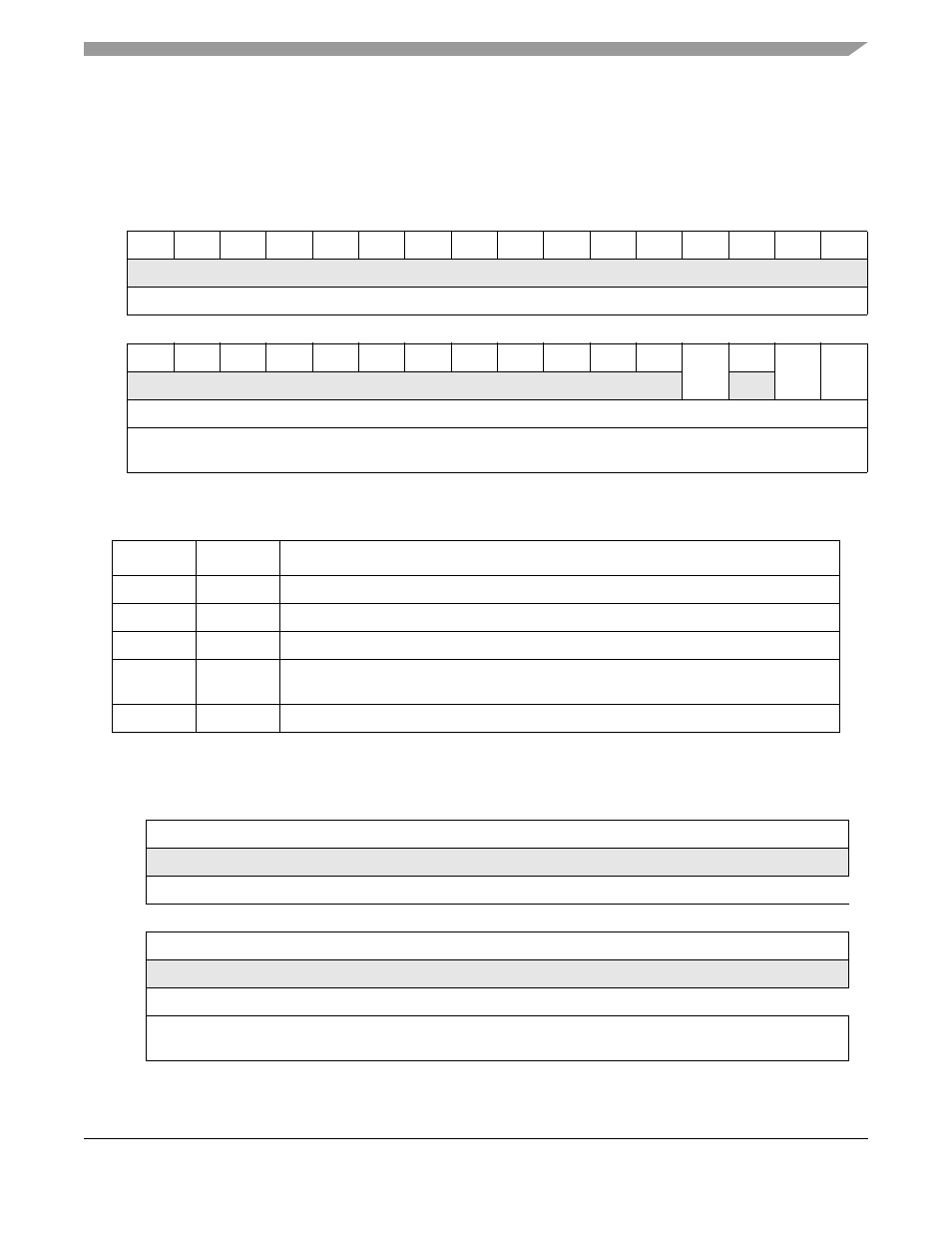

Reset Status Register (RSR)

RSR allows the software, particularly the reset exception service routine, to know what type of reset has

been asserted. When a reset signal is asserted, the associated status bit is set, and it maintains its value until

the software explicitly clears the bit.

9.3.1.4

JTAG Device Identification Number (JTAGID)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

RST

JTG

0

RST

WD

RST

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

Reg

Addr

MBAR + 0x44

Figure 9-4. Reset Status Register (RSR)

Table 9-4. RSR Field Descriptions

Bits

Name

Description

31–4

—

Reserved, should be cleared.

3

RSTJTG

JTAG reset asserted. Cleared by writing 1 to this bit position or by external reset.

2

—

Reserved, should be cleared.

1

RSTWD

General purpose watchdog timer reset asserted. Cleared by writing 1 to this bit position or

by external reset.

0

RST

External reset (PLL Lock qualification) asserted. Cleared by writing a 1 to this bit position.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

JTAGID

W

Reset

See

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

JTAGID

W

Reset

See

Reg

Addr

MBAR + 0x50

Figure 9-5. JTAG Device ID Register (JTAGID)