Table 2-1/2-3 – Freescale Semiconductor MCF5480 User Manual

Page 73

Introduction

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

2-3

lists the signals for the MCF548x in functional group order.

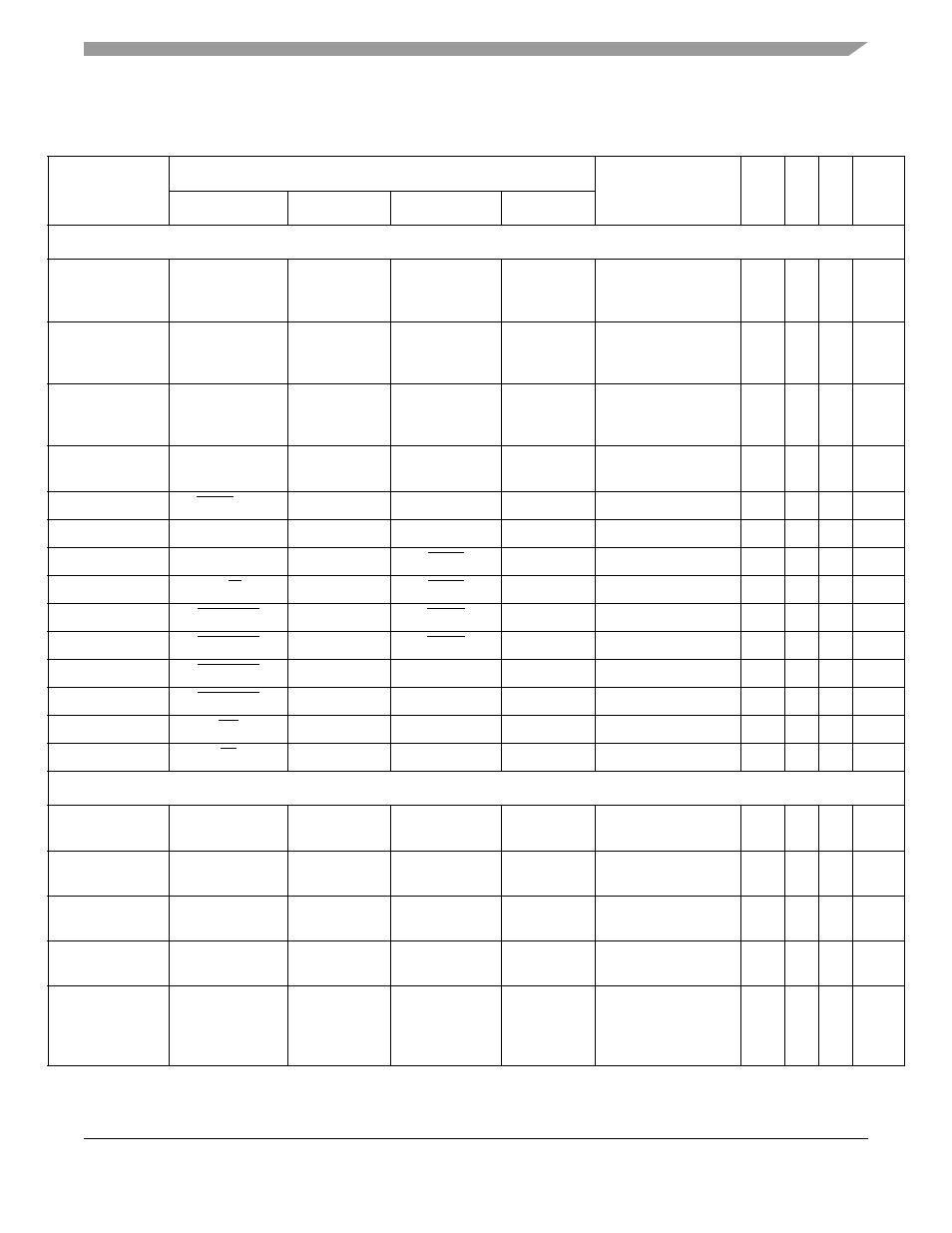

Table 2-1. MCF548x Signal Description

PBGA Pin

Pin Functions

Description

I/O

Pu

ll-u

p

Drive

Res

e

t

St

a

te

Primary

GPIO

Secondary

Tertiary

FlexBus

AE2, AF3, AF1,

AE3, AE4, AD5,

AF2, AD4

AD[31:24]

—

—

—

Multiplexed

address/data bus

I/O

16

Hi-Z

AD3, AC3, AD2,

AC2, AA4, AE1,

AC1, AD1

AD[23:16]

—

—

—

Multiplexed

address/data bus

I/O

16

Hi-Z

AB2, AA3, W4,

AB1, AA2, AA1,

Y1, Y2

AD[15:8]

—

—

—

Multiplexed

address/data bus

I/O

16

Hi-Z

W3, W1, W2, V3,

V1, V2, T4, U3

AD[7:0]

—

—

—

Multiplexed

address/data bus

I/O

16

Hi-Z

R1, T2, T3, T1, U2

FBCS[5:1]

PFBCS[5:1]

—

—

Chip selects 5–1

O:I/O

24

High

U1

FBCS0

—

—

—

Chip select 0

O

24

High

AD6

ALE

PFBCTL0

TBST

—

Address Latch Enable O:I/O

16

High

AE5

R/W

PFBCTL2

TBST

—

Read/write

O:I/O

16

Hi-Z

AF4

BE/BWE3

PFBCTL7

TSIZ1

—

Byte enables

O:I/O

16

High

AF5

BE/BWE2

PFBCTL6

TSIZ0

—

Byte enables

O:I/O

16

High

AC4

BE/BWE1

PFBCTL5

FBADDR1

—

Byte enables

O:I/O

16

High

AE7

BE/BWE0

PFBCTL4

FBADDR0

—

Byte enables

O:I/O

16

High

AE6

OE

PFBCTL3

—

—

Output enable

O:I/O

16

High

AF6

TA

PFBCTL1

—

—

Transfer acknowledge

I:I/O

16

—

SDRAM Controller

C10, B9, A8, D5,

A6, C8, B7, A5

SDDATA[31:24]

—

—

—

SDRAM data bus

I/O

24

Hi-Z

A4, C7, B6, B4,

C5, B3, C4, D4

SDDATA[23:16]

—

—

—

SDRAM data bus

I/O

24

Hi-Z

E2, D1, G4, E1,

K4, F1, G2, H3

SDDATA[15:8]

—

—

—

SDRAM data bus

I/O

24

Hi-Z

N4, G1, H2, J3,

J1, M4, K3, K2

SDDATA[7:0]

—

—

—

SDRAM data bus

I/O

24

Hi-Z

A13, A12, D10,

B12, C12, A11,

D8, B11, C11,

A10, D7, B10, A9

SDADDR[12:0]

—

—

—

SDRAM address bus

O

24

Low