2 external signals, 3 memory map/register definition, External signals -2 – Freescale Semiconductor MCF5480 User Manual

Page 342: Memory map/register definition -2

MCF548x Reference Manual, Rev. 3

11-2

Freescale Semiconductor

6. Watchdog Timer—This is a special CPU timer mode, available only on GPT0. The user must

enable the watchdog timer mode, which is not active upon reset. The terminal count value is

programmable. If the counter is allowed to expire, a full reset occurs. To prevent the watchdog

timer from expiring, software must periodically write 0xA5 to the GMS0[OCPW] field. This

causes the counter to reset.

11.2

External Signals

The GPT signals are the following:

•

TIN[3:0]—External timer input

•

TOUT[3:0]—External timer output

11.3

Memory Map/Register Definition

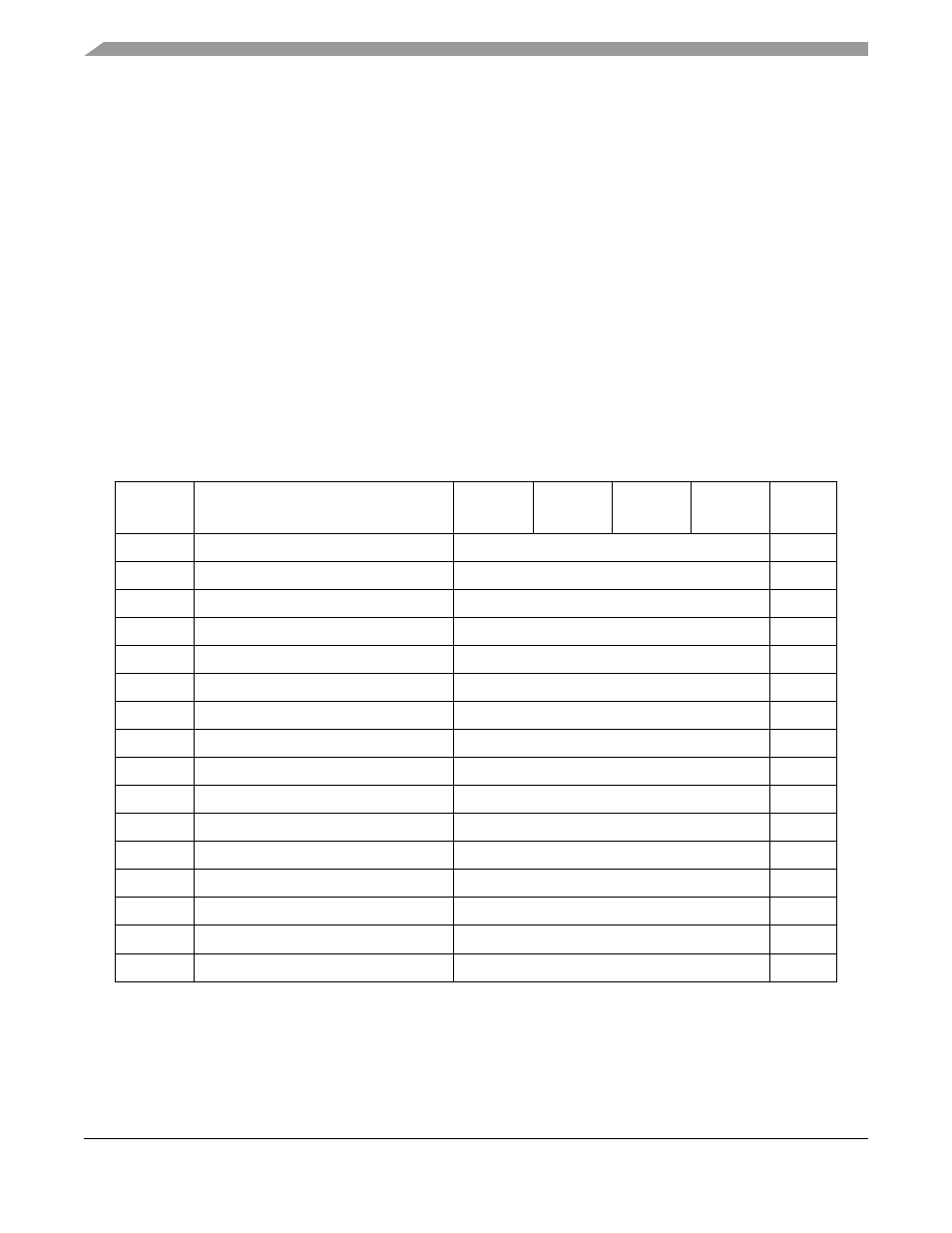

Each GPT uses four 32-bit registers. These registers are located at MBAR + the GPT offset 0x800.

summarizes the GPT control registers.

Table 11-1. General Purpose Timer Memory Map

Address

(MBAR +)

Name

Byte 0

Byte 1

Byte 2

Byte 3

Access

0x800

GPT Enable and Mode Select Register 0

GMS0

R/W

0x804

GPT Counter Input Register 0

GCIR0

R/W

0x808

GPT PWM Configuration Register 0

GPWM0

R/W

0x80C

GPT Status Register 0

GSR0

R

0x810

GPT Enable and Mode Select Register 1

GMS1

R/W

0x814

GPT Counter Input Register 1

GCIR1

R/W

0x818

GPT PWM Configuration Register 1

GPWM1

R/W

0x81C

GPT Status Register 1

GSR1

R

0x820

GPT Enable and Mode Select Register 2

GMS2

R/W

0x824

GPT Counter Input Register 2

GCIR2

R/W

0x828

GPT PWM Configuration Register 2

GPWM2

R/W

0x82C

GPT Status Register 2

GSR2

R

0x830

GPT Enable and Mode Select Register 3

GMS3

R/W

0x834

GPT Counter Input Register 3

GCIR3

R/W

0x838

GPT PWM Configuration Register 3

GPWM3

R/W

0x83C

GPT Status Register 3

GSR3

R