Freescale Semiconductor MCF5480 User Manual

Page 74

MCF548x Reference Manual, Rev. 3

2-4

Freescale Semiconductor

M2, M3

SDBA[1:0]

—

—

—

SDRAM bank

addresses

O

24

Low

E3

RAS

—

—

—

SDRAM row address

strobe

O

24

High

C2

CAS

—

—

—

SDRAM column

address strobe

O

24

High

R2, P2, P1, N3

SDCS[3:0]

—

—

—

SDRAM chip selects

O

24

High

B8, A3, G3, J2

SDDM[3:0]

—

—

—

SDRAM write data

byte mask

O

24

High

A7, B5, F2, H1

SDDQS[3:0]

—

—

—

SDRAM data strobe

I/O

24

High

L1, N1

SDCLK[1:0]

—

—

—

SDRAM clock

O

24

Low

M1, N2

SDCLK[1:0]

—

—

—

Inverted SDRAM

clock

O

24

Low

K1

SDWE

—

—

—

SDRAM write enable

O

24

Low

E4

SDCKE

—

—

—

SDRAM clock enable

O

24

Low

L2

SDRDQS

—

—

—

SDR SDRAM data

strobe

O

24

Low

D2

VREF

—

—

—

SDRAM reference

voltage

I

—

—

PCI Controller

V25, V26, U25,

U26, T24, T25,

T26, R24

PCIAD[31:24]

—

FBADDR[31:24]

—

PCI address/data bus

I/O

16

Hi-Z

R25, R26, P26,

P24, P23, P25,

N25, N23

PCIAD[23:16]

—

FBADDR[23:16]

—

PCI address/data bus

I/O

16

Hi-Z

N26, N24, M26,

M25, L26, L25,

K26, K25

PCIAD[15:8]

—

FBADDR[15:8]

—

PCI address/data bus

I/O

16

Hi-Z

J26, K24, J25,

H26, J24, G26,

H25, K23

PCIAD[7:0]

—

FBADDR[7:0]

—

PCI address/data bus

I/O

16

Hi-Z

F26, G25, E26,

G24

PCICXBE[3:0]

—

—

—

PCI command/byte

enables

I/O

16

Hi-Z

J23

PCIDEVSEL

—

—

—

PCI device select

I/O

16

Hi-Z

F25

PCIFRM

—

—

—

PCI frame

I/O

16

Hi-Z

C23

PCIIDSEL

—

—

—

PCI initialization

device select

I

—

—

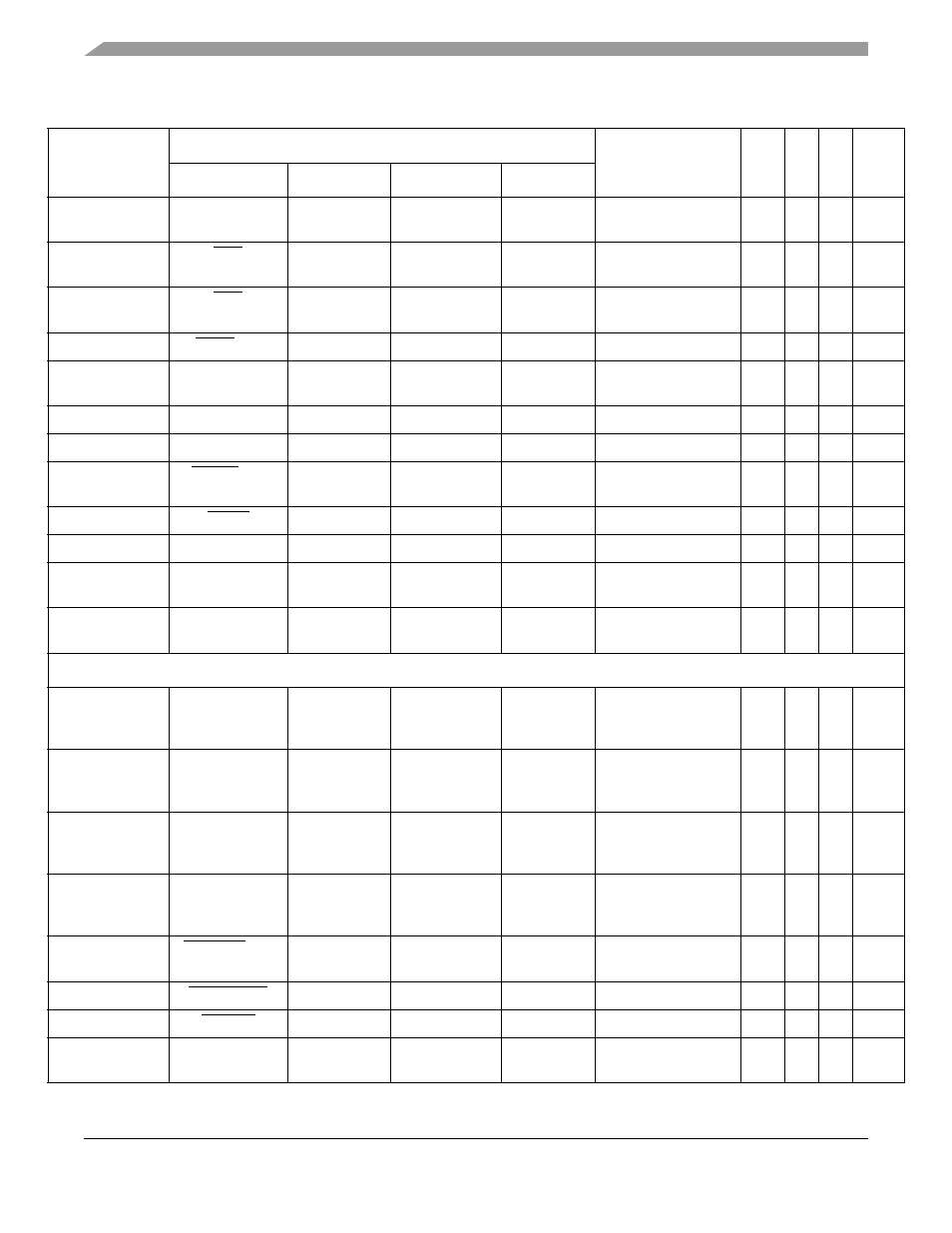

Table 2-1. MCF548x Signal Description (Continued)

PBGA Pin

Pin Functions

Description

I/O

Pu

ll-u

p

Drive

Res

e

t

St

a

te

Primary

GPIO

Secondary

Tertiary