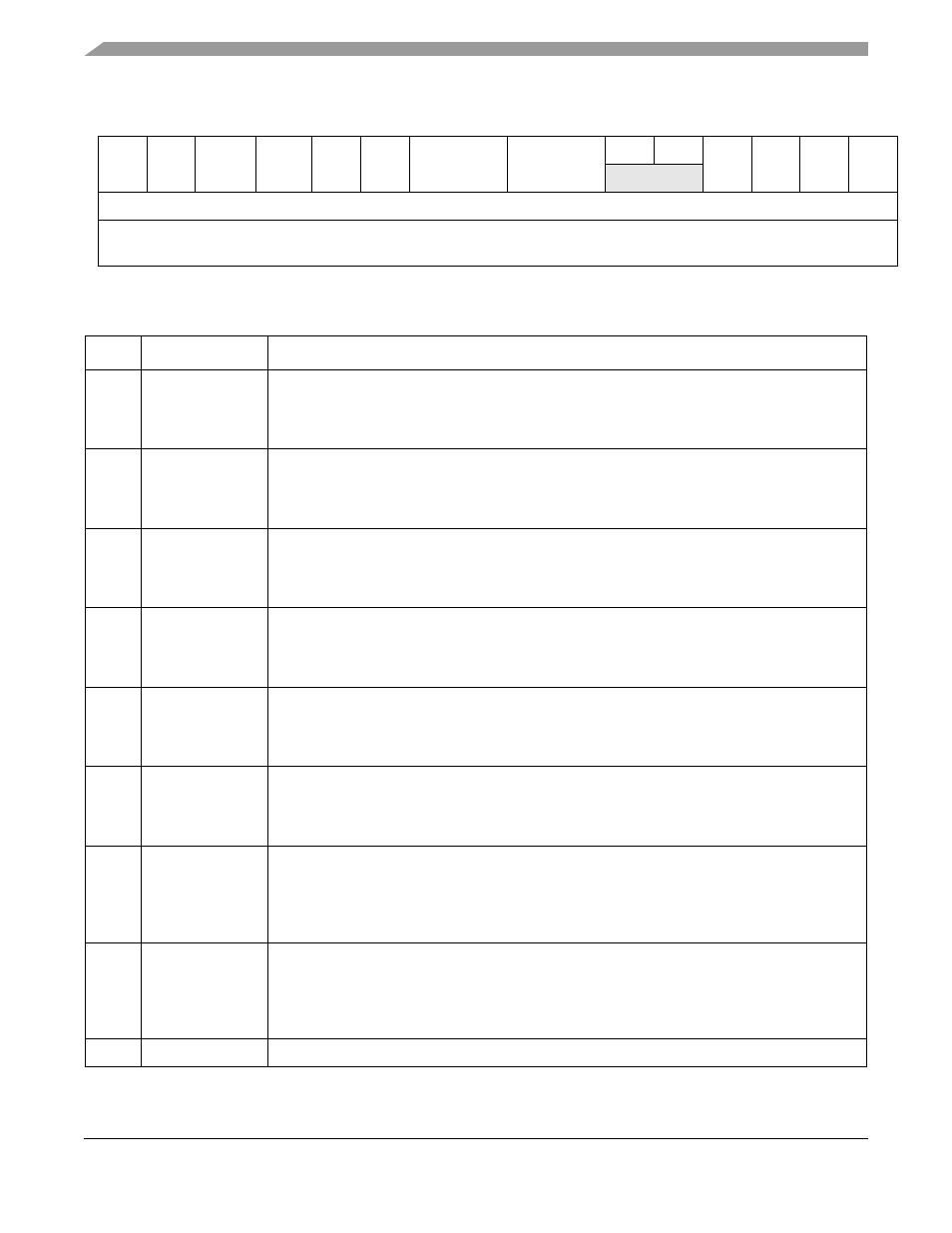

Table 15-27/15-24 – Freescale Semiconductor MCF5480 User Manual

Page 396

MCF548x Reference Manual, Rev. 3

15-24

Freescale Semiconductor

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R PAR_

E07

PAR_

E0MII

PAR_

E0MDIO

PAR_

E0MDC

PAR_

E17

PAR_

E1MII

PAR_E1MDIO PAR_E1MDC

0

0

PAR_

SDA

PAR_

SCL

PAR_

IRQ6

PAR_

IRQ5

W

Reset

0

0

0

0

0

0

1

1

1

1

0

0

0

0

1

1

Reg

Addr

MBAR + 0xA44 (PAR_FECI2CIRQ)

Figure 15-25. FEC/I2C/IRQ Pin Assignment Register (PAR_FECI2CIRQ)

Table 15-27. PAR_FEC/I2C/IRQ Field Descriptions

Bits

Name Description

15

PAR_E07

FEC0 7-wire mode pin assignment. Configures all the FEC0 7-wire mode pins (port FEC0H pins,

except for E0CRS) for their primary functions or general purpose I/O.

0 All FEC1 7-wire mode pins configured for GPIO (PFEC0H[7:1])

1 All FEC1 7-wire mode pins configured for their primary functions

14

PAR_E0MII

FEC1 MII mode-only pin assignment. Configures all the FEC0 MII mode-only pins (port FEC0L

pins, plus FEC0_CRS) for their primary functions or general purpose I/O.

0 All FEC0 MII mode-only pins configured for GPIO (PFEC0H0 and PFEC0L[7:0]

1 All FEC0 MII mode-only pins configured for their primary functions

13

PAR_E0MDIO

FEC0 MDIO pin assignment. Configures the E0MDIO pin for its primary function or general

purpose I/O.

0 E0MDIO pin configured for GPIO (PFECI2C3)

1 E0MDIO pin configured for E0MDIO function

12

PAR_E0MDC

FEC0 MDC pin assignment. Configures the E0MDC pin for its primary function or general

purpose I/O.

0 E0MDC pin configured for GPIO (PFECI2C2)

1 E0MDC pin configured for E0MDC function

11

PAR_E17

FEC1 7-wire mode pin assignment. Configures all the FEC1 7-wire mode pins (port FEC1H pins,

except for E1CRS) for their primary functions or general purpose I/O.

0 All FEC1 7-wire mode pins configured for GPIO (PFEC1H[7:1])

1 All FEC1 7-wire mode pins configured for their primary functions

10

PAR_E1MII

FEC1 MII mode-only pin assignment. Configures all the FEC1 MII mode-only pins (port FEC1L

pins, plus E1CRS) for their primary functions or general purpose I/O.

0 All FEC1 MII mode-only pins configured for GPIO (PFEC1H0 and PFEC1L[7:0])

1 All FEC1 MII mode-only pins configured for their primary functions

9–8

PAR_

E1MDIO

FEC1 MDIO pin assignment. Configures the E1MDIO pin for one of its primary functions. There

is no GPIO capability on this pin.

0X E1MDIO pin configured for FlexCAN CANRX0

10 E1MDIO pin configured for I2C SDA function

11 E1MDIO pin configured for FEC1 E1MDIO function

7–6

PAR_

E1MDC

FEC1 MDC pin assignment. Configures the E1MDC pin for one of its primary functions. There is

no GPIO capability on this pin.

0X E1MDC pin configured for FlexCAN CANTX0

10 E1MDC pin configured for I2C SCL function

11 E1MDC pin configured for FEC1 E1MDC function

5–4

—

Reserved, should be cleared.