1 dspi module configuration register (dmcr), Dspi module configuration register (dmcr) -5 – Freescale Semiconductor MCF5480 User Manual

Page 823

Memory Map and Registers

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

27-5

27.6.1

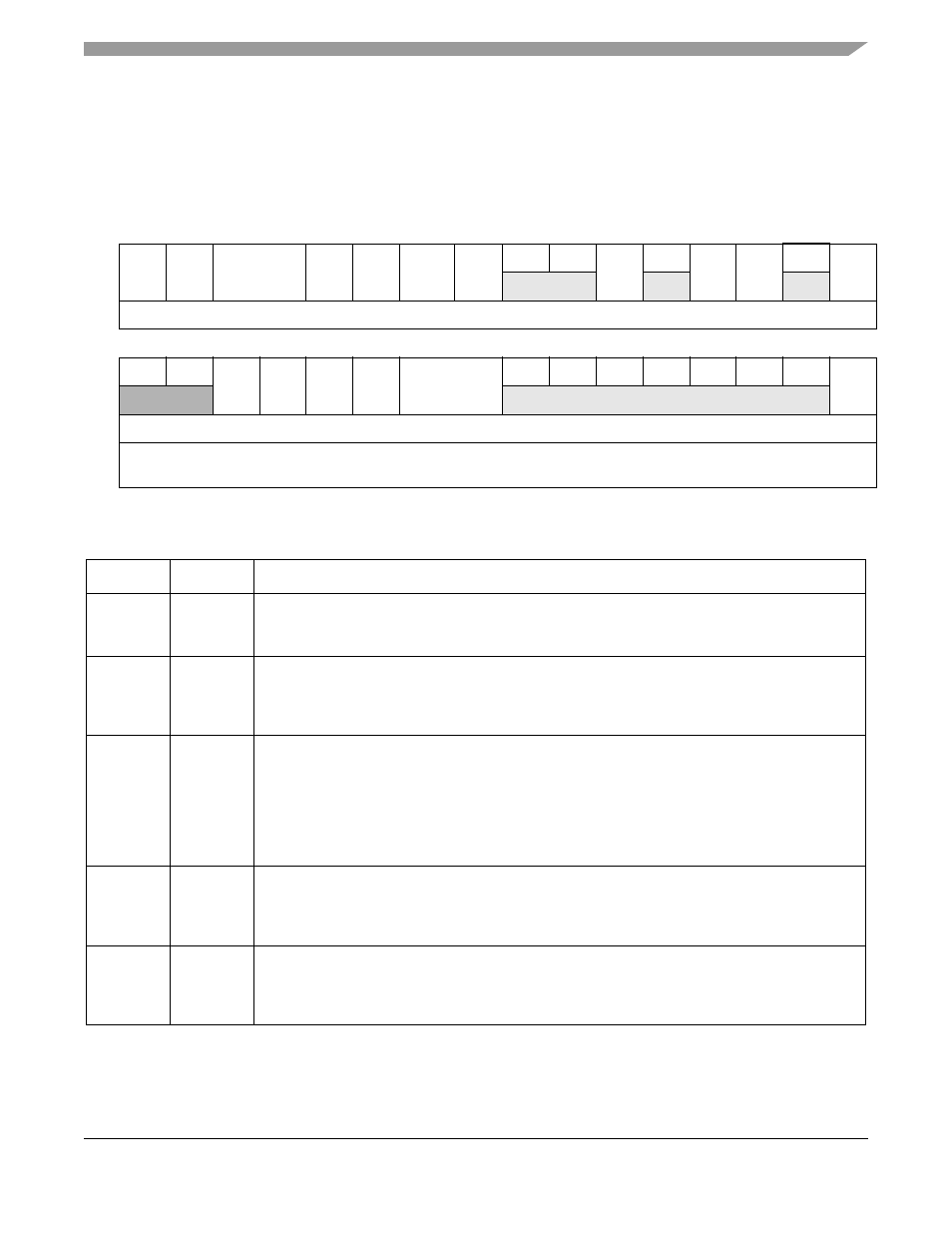

DSPI Module Configuration Register (DMCR)

The DMCR contains bits which configure various attributes associated with DSPI operation. The HALT

bit can be changed at any time but will only take effect on the next frame boundary.

Only the HALT bit in the DMCR may be changed while the DSPI is in the running state.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R MSTR CSCK

DCONF

FRZ

MTFE PCSSE ROOE

0

0

CSIS5

0

CSIS3 CSIS2

0

CSIS0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

DTXF DRXF CTXF CRXF

SMPL_PT

0

0

0

0

0

0

0

HALT

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x8A00

Figure 27-2. DSPI Module Configuration Register (DMCR)

Table 27-3. DMCR Field Descriptions

Bits

Name

Description

31

MSTR

Master/Slave mode select. Configures the DSPI for either master mode or slave mode.

0 DSPI is in slave mode

1 DSPI is in master mode

30

CSCK

Continuous DSPISCK enable. Enables the DSPISCK clock to run continuously. See

Section 27.7.5, “Continuous Serial Communications Clock

” for details.

0 Continuous DSPISCK disabled

1 Continuous DSPISCK enabled

29–28

DCONF

DSPI configuration. Selects between the three different configurations of the DSPI.

00 SPI

01 Reserved

10 Reserved

11 Reserved

Note: All values except 00 are reserved. This field must be configured for SPI mode for the DSPI

module to operate correctly.

27

FRZ

Freeze. Enables the DSPI transfer to be stopped on the next frame boundary when the device is

halted in debug mode.

0 Do not halt serial transfers

1 Halt serial transfers

26

MTFE

Modified timing format enable. Enables a modified transfer format to be used. See

“Modified SPI Transfer Format (MTFE = 1, CPHA = 1)

” for more information.

0 Modified SPI transfer format disabled

1 Modified SPI transfer format enabled