1 arbiter configuration register (xarb_cfg), Arbiter configuration register (xarb_cfg) -9 – Freescale Semiconductor MCF5480 User Manual

Page 331

XL Bus Arbiter

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

10-9

10.3.3.1

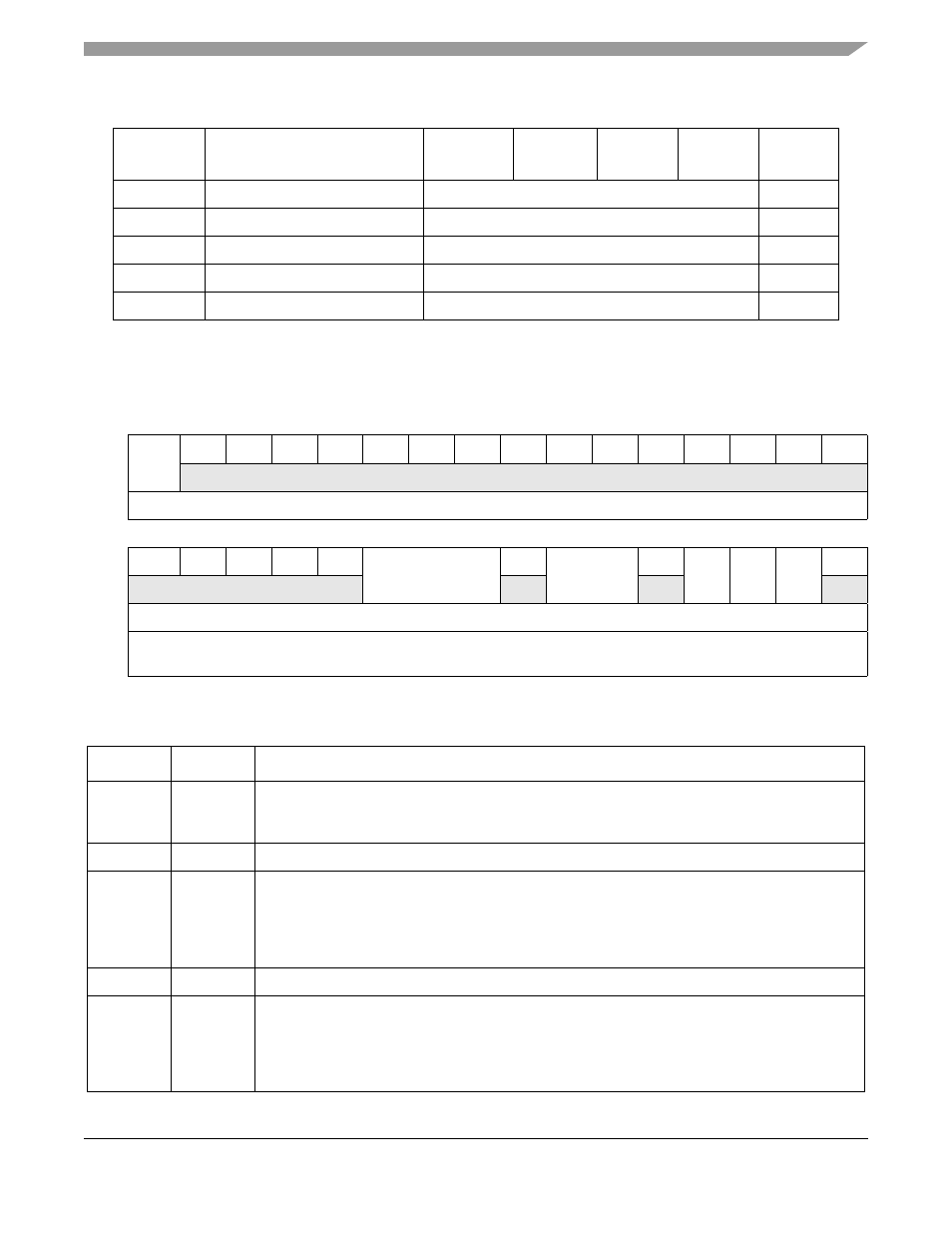

Arbiter Configuration Register (XARB_CFG)

The arbiter configuration register is used to enable watchdog functions and arbiter protocol functions.

0x258

Arbiter Address Timeout

XARB_ADRTO

R/W

0x25C

Arbiter Data Timeout

XARB_DATTO

R/W

0x260

Arbiter Bus Timeout

XARB_BUSTO

R/W

0x264

Arbiter Master Priority Enable

XARB_PRIEN

R/W

0x268

Arbiter Master Priority

XARB_PRI

R/W

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R PLDIS

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

SP

0

PM

0

BA

DT

AT

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

Reg

Addr

MBAR + 0x0240

Figure 10-5. Arbiter Configuration Register (XARB_CFG)

Table 10-5. XARB_CFG Bit Descriptions

Bit

Name

Description

31

PLDIS

Pipeline Disable. This bit is used to control the pipeline functionality

0 Enable pipeline

1 Disable pipeline

30–11

—

Reserved, should be cleared.

10–8

SP

Select Parked Master. These bits set the master that is used in Park on Programmed Master mode.

000 Master 0

001 Master 1

...

111 Master 7).

7

—

Reserved, should be cleared.

6–5

PM[1:0]

Parking Mode. Parking modes are detailed in

Section 10.3.2.2.2, “Parking Modes.”

00 No parking (default)

01 Reserved

10 Park on most recently used master

11 Park on programmed master as specified by the Select Parked Master bits 21:23 above.

Table 10-4. XL Bus Arbiter Memory Map (Continued)

MBAR

Offset

Name

Byte0

Byte1

Byte2

Byte3

Access