5 deu interrupt mask register (dimr), Deu interrupt mask register (dimr) -39, P. 22-39 – Freescale Semiconductor MCF5480 User Manual

Page 641

Data Encryption Standard Execution Units (DEU)

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

22-39

22.9.5

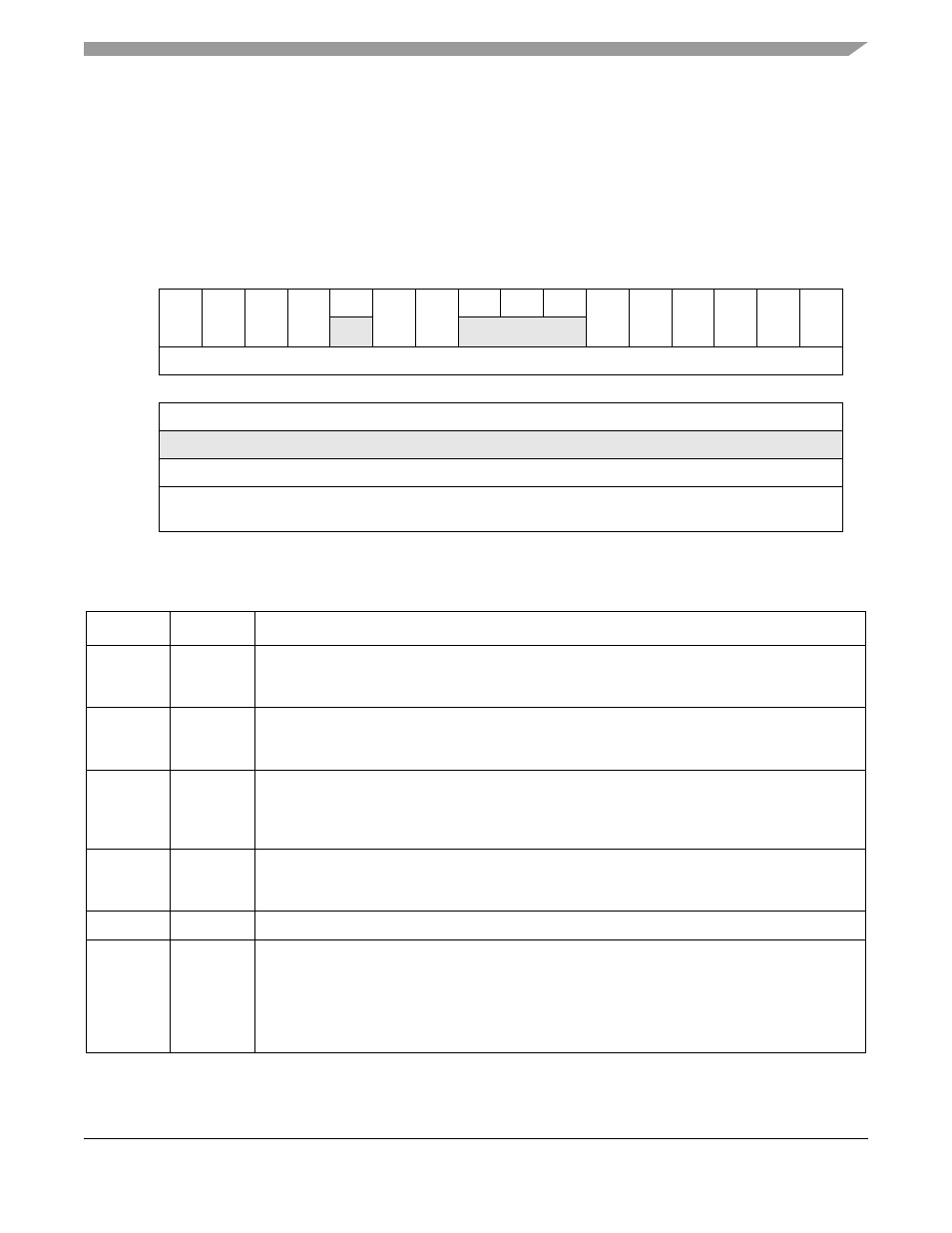

DEU Interrupt Mask Register (DIMR)

The interrupt mask register controls the result of detected errors. For a given error (as defined in

Section 22.9.4, “DEU Interrupt Status Register (DISR)

”), if the corresponding bit in this register is set,

then the error is ignored; no error interrupt occurs and the interrupt status register is not updated to reflect

the error. If the corresponding bit is not set, then upon detection of an error, the interrupt status register is

updated to reflect the error, causing assertion of the error interrupt signal, and causing the module to halt

processing.

Figure 22-28. DEU Interrupt Mask Register (DIMR)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

ME

AE

OFE

IFE

0

IFO

OFU

0

0

0

KPE

IE

ERE

CE

KSE

DSE

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

AFEU 0x2A038

Table 22-25. DIMR Field Descriptions

Bits

Name

Description

31

ME

Mode error. An illegal value was detected in the mode register.

0 Mode error enabled

1 Mode error disabled

30

AE

Address error. An illegal read or write address was detected within the DEU address space.

0 Address error enabled

1 Address error disabled

29

OFE

Output FIFO error. The DEU output FIFO was detected non-empty upon write of DEU data size

register

0 Output FIFO non-empty error enabled

1 Output FIFO non-empty error disabled

28

IFE

Input FIFO error. The DEU input FIFO was detected non-empty upon generation of done interrupt

0 Input FIFO non-empty error enabled

1 Input FIFO non-empty error disabled

27

—

Reserved

26

IFO

Input FIFO overflow. The DEU input FIFO has been pushed while full.

0 Input FIFO overflow error enabled

1 Input FIFO overflow error disabled

Note: When operating as a master, the implements flow-control, and FIFO size is not a limit to data

input. When operated as a target, the cannot accept FIFO inputs larger than 512 bytes without

overflowing.