Freescale Semiconductor MCF5480 User Manual

Page 771

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

26-9

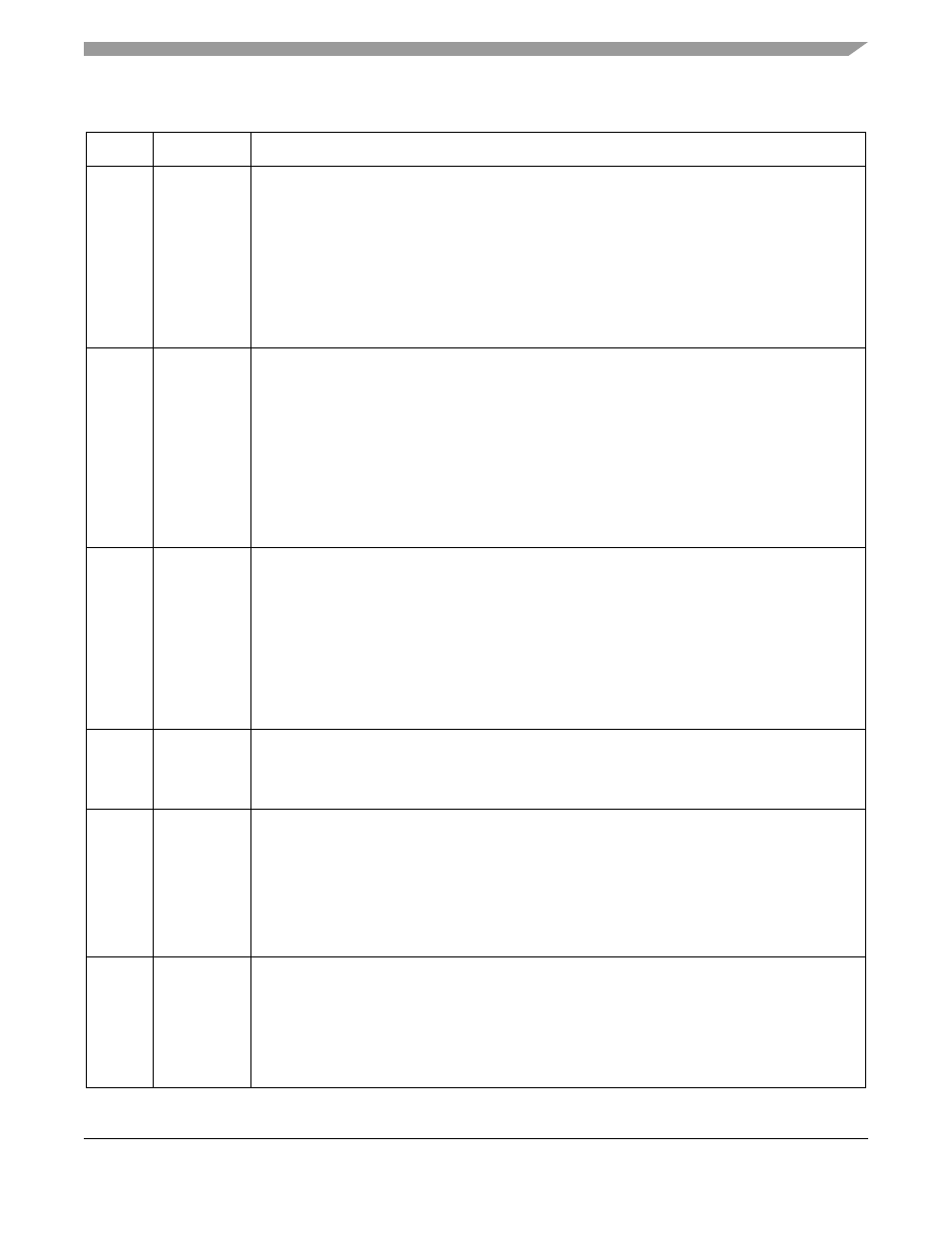

Table 26-5. PSCSRn Field Descriptions

Bits

Name

Description

15

RB_NEOF

For UART and SIR modes, this field signifies a received break.

0 No break received.

1 Break received.

For modem mode, this field is reserved.

In MIR and FIR mode, this bit signifies a next byte is EOF.

0 The next byte to be read from the RxFIFO is not the last one of the frame.

1 The next byte to be read from the RxFIFO is the last one of the frame. This bit is effective when

RxRDY = 1.

14

FE_PHYERR For UART and SIR modes, this field signifies a framing error.

0 No error.

1 The stop bits are not correct.

In modem mode, this bit is reserved.

In MIR and FIR mode, this bit signifies a Physical layer error.

0 No error

1 In MIR mode, this denotes that the receiver received an abort. In FIR mode, this denotes that

there was a decode error. This bit can be cleared by the reset error status command in the

PSCCR.

13

PE_CRCERR For UART and SIR modes, this field signifies a parity error.

0 Parity error has not occurred.

1 Parity error has occurred.

In modem mode, this bit is reserved.

In MIR and FIR mode, this bit signifies a CRC error.

0 No error

1 The CRC value was not correct. This bit can be cleared by the reset error command in the

PSCCR.

12

OE

For all modes, this field signifies an overrun error occurred.

0 No error.

1 One or more received characters have been lost. This bit is cleared by the reset error command

in CR.

11

TXEMP_

URERR

For UART and SIR modes, this field signifies a transmitter empty.

0 The transmitter is busy or there is at least one data in the TxFIFO.

1 The transmitter and the TxFIFO is empty.

In modem and MIR and FIR modes, this bit signifies an underrun error.

0 No error.

1 Underrun error occurred. When the transmitter intended to send, there was no data in the

TxFIFO. This bit is cleared by the reset error command in the PSCCR.

10

TXRDY

For all modes, this field signifies a Transmitter ready.

0 The number of the data in the TxFIFO is more than the threshold. Different from FIFO’s alarm,

this bit is determined only by the threshold and not by the granularity.

1 The number of data in the TxFIFO is less than or equal to the threshold (TFALARM). In UART

and SIR mode, this bit becomes asserted only when the transmitter is enabled. On the contrary,

in modem mode and MIR and FIR IrDA mode, this bit becomes asserted even if the transmitter

is disabled.