Table 8-8 describes csr fields – Freescale Semiconductor MCF5480 User Manual

Page 262

MCF548x Reference Manual, Rev. 3

8-12

Freescale Semiconductor

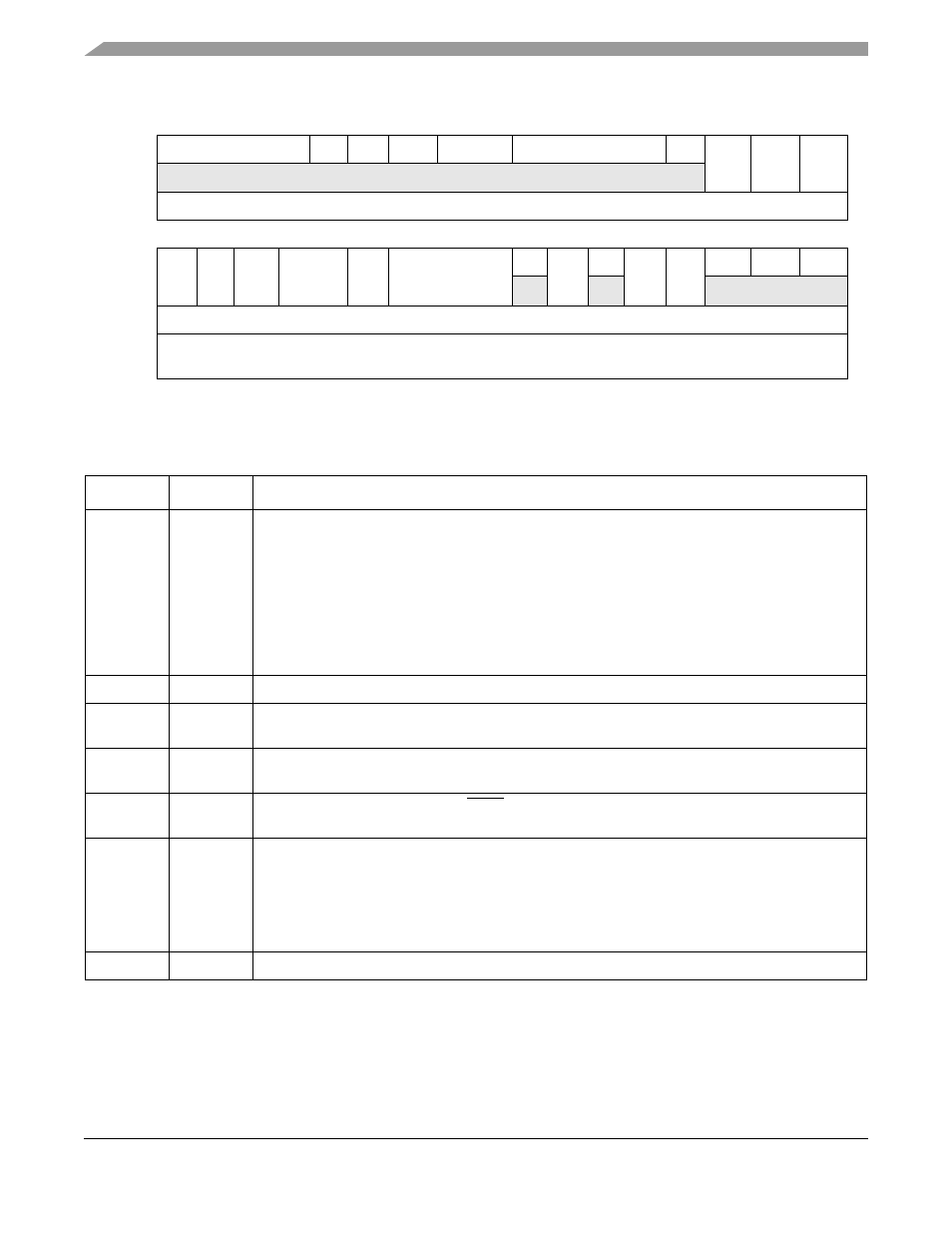

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

BSTAT

FOF TRG HALT

BKPT

HRL

0

BKD0 PCD0 IPW0

W

Reset

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R MAP TRC EMU

DDC

UHE

BTB

0

NPL

0

SSM OTE

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

CPU + 0x00

Figure 8-6. Configuration/Status Register (CSR)

Table 8-8. CSR Field Descriptions

Bits

Name

Description

31–28

BSTAT

Breakpoint status. Provides read-only status information concerning hardware breakpoints. Also

output on PSTDDATA when it is not displaying PST or other processor data. BSTAT is cleared by a

TDR or XTDR write or by a CSR read when either a level-2 breakpoint is triggered or a level-1

breakpoint is triggered and the level-2 breakpoint is disabled.

0000 No breakpoints enabled

0001 Waiting for level-1 breakpoint

0010 Level-1 breakpoint triggered

0101 Waiting for level-2 breakpoint

0110 Level-2 breakpoint triggered

27

FOF

Fault-on-fault. If FOF is set, a catastrophic halt occurred and forced entry into BDM.

26

TRG

Hardware breakpoint trigger. If TRG is set, a hardware breakpoint halted the processor core and

forced entry into BDM. Reset, and the debug

GO

command clear TRG.

25

HALT

Processor halt. If HALT is set, the processor executed a HALT and forced entry into BDM. Reset,

and the debug

GO

command clear HALT.

24

BKPT

Breakpoint assert. If BKPT is set, BKPT is asserted, forcing the processor into BDM. Reset, and

the debug

GO

command clear BKPT.

23–20

HRL

Hardware revision level. Indicates the level of debug module functionality. An emulator could use

this information to identify the level of functionality supported.

0000 Initial debug functionality (Revision A)

0001 Revision B

0010 Revision C

0011 Revision D

19

—

Reserved, should be cleared.