2 transfer count configuration register (tccr), Transfer count configuration register (tccr) -4 – Freescale Semiconductor MCF5480 User Manual

Page 412

MCF548x Reference Manual, Rev. 3

16-4

Freescale Semiconductor

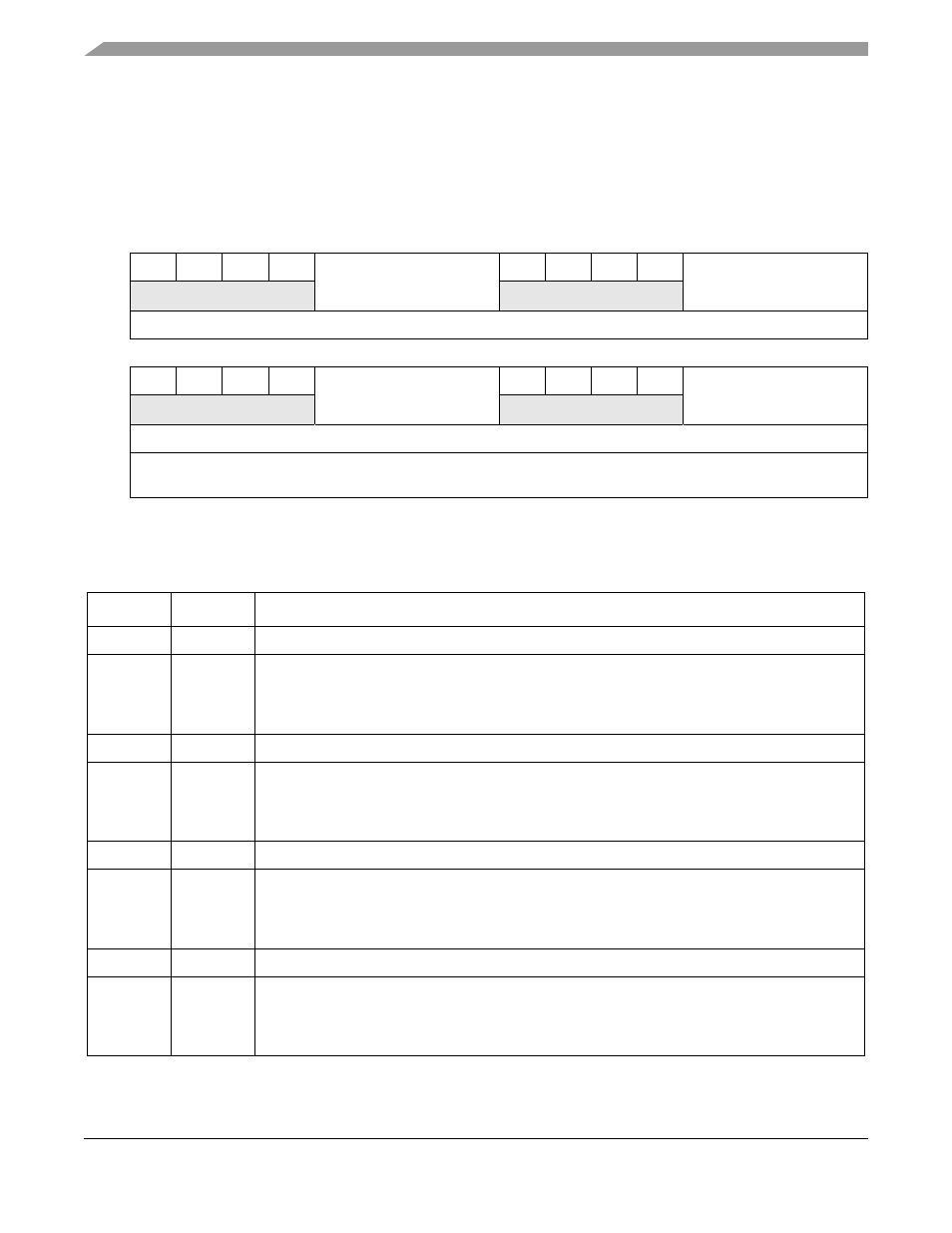

16.2.2

Transfer Count Configuration Register (TCCR)

This register is used to configure the allocated maximum transfer count for each bank for the following

masters: the ColdFire core, DMA, SEC, or PCI. This occurs as they access memory through the shared

system bus. The DMA and the SEC can access the system SRAM either via the system bus or via their

dedicated ports. Refer to sections 16.2.3 through 16.2.5.

Each field is described in the

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

BANK3_TC

0

0

0

0

BANK2_TC

W

Reset

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

BANK1_TC

0

0

0

0

BANK0_TC

W

Reset

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

Reg

Addr

MBAR + 0x1_FFC4

Figure 16-3. Transfer Count Configuration Register (TCCR)

Table 16-3. TCCR Register Field Descriptions

Bits

Name Description

31–28

—

Reserved, should be cleared.

27–24

BANK3_TC Bank three transfer count. This field indicates the maximum transfer count for bank 3. The master

can make at most 4 * {field value} 32-bit transfers to/from bank 3 before it must wait for other

masters to complete their transfers. If this field is programmed to “0” the master can “own” bank 3

for arbitrarily long transfers.

23–20

—

Reserved, should be cleared.

19–16

BANK2_TC Bank two transfer count. This field indicates the maximum transfer count for bank 2. The master

can make at most 4 * {field value} 32-bit transfers to/from bank 2 before it must wait for other

masters to complete their transfers. If this field is programmed to “0” the master can “own” bank 2

for arbitrarily long transfers.

15–12

—

Reserved. Should be cleared.

11–8

BANK1_TC Bank one transfer count. This field indicates the maximum transfer count for bank 1. The master

can make at most 4 * {field value} 32-bit transfers to/from bank 1 before it must wait for other

masters to complete their transfers. If this field is programmed to “0” the master can “own” bank 1

for arbitrarily long transfers.

7–4

—

Reserved. Should be cleared.

3–0

BANK0_TC Bank zero transfer count. This field indicates the maximum transfer count for bank 0. The master

can make at most 4 * {field value} 32-bit transfers to/from bank 0 before it must wait for other

masters to complete their transfers. If this field is programmed to “0” the master can “own” bank 0

for arbitrarily long transfers.