Figure 30-23, And the fields are further defi, Table 30-27 – Freescale Semiconductor MCF5480 User Manual

Page 959

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

30-29

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

TIMER FRM

EN

GR

IP_

MSK

FAE_

MSK

RXW_

MSK

UF_

MSK

OF_

MSK

1

0

0

W

Reset

0

0

0

0

0

0

0

1

0

0

1

0

0

1

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

COUNTER

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

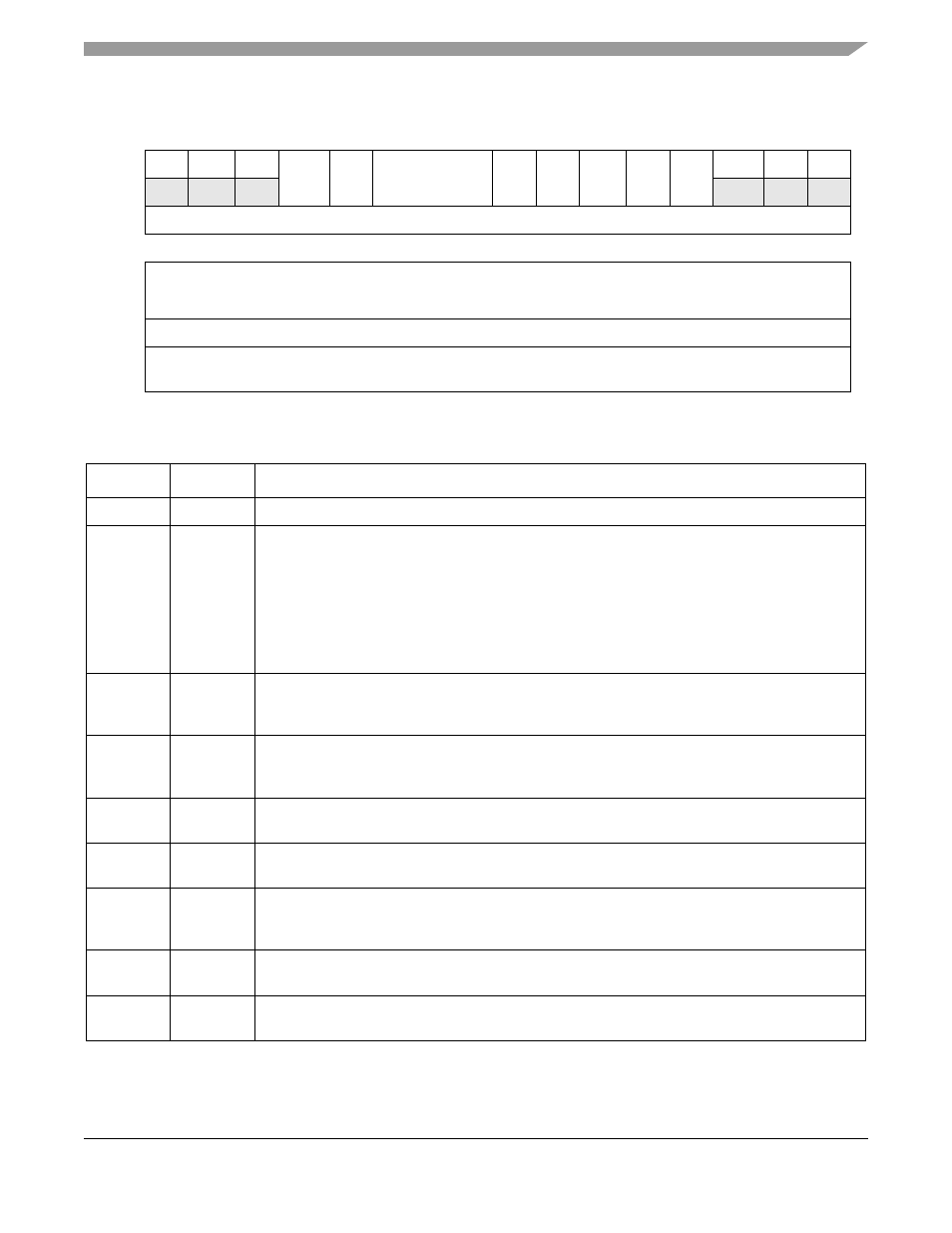

Reg

Addr

MBAR + 0x918C (FEC0), 0x998C (FEC1)

Figure 30-23. FEC Receive FIFO Control Register (FECRFCR)

Table 30-27. FECRFCR Field Descriptions

Bits

Name

Descriptions

31–29

—

Reserved, should be cleared.

28

TIMER

Timer mode enable. When this bit is set, the FIFO controller will suppress a frame ready request

for service from occuring until the timer expires. The timer period can be programmed using the

COUNTER[15:0] bits. A request for service will be made every (COUNTER[15:0] * 64) cycles as

long as a valid frame exists in the FIFO. Alarm requests are not affected by this mode. Further, the

timer is restarted anytime a read or a write to the FIFO Data register occurs. This indicates that

either the FIFO currently has the DMA’s attention or that data is still being transferred and that there

is the possibility that a naturally generated alarm will occur. This bit is only meaningful when frame

mode is enabled via the FRMEN bit.

27

FRMEN

Frame mode enable. When this bit is set, the FIFO controller monitors frame done information from

the peripheral or multi-channel DMA. Setting this bit also enables the other frame control bits in this

register, as well as other frame functions. This bit must be set to use frame functions.

26–24

GR

Last transfer granularity. These bits define the deassertion point for the “high” service request. A

“high” service request is deasserted when there are less than GR[2:0] data bytes remaining in the

FIFO.

23

IP_MSK

llegal pointer mask. When this bit is set, the FIFO controller masks the status register’s IP bit from

generating a RFERR in the EIR.

22

FAE_MSK

Frame accept error mask. When this bit is set, the FIFO controller masks the status register’s FAE

bit from generating a RFERR in the EIR.

21

RXW_MSK Receive wait condition mask. When this bit is set, the FIFO controller masks the status register’s

RXW bit from generating a RFERR in the EIR. (To help with backward compatibility, this bit is set

at reset.)

20

UF_MSK

FIFO underflow mask. When this bit is set, the FIFO controller masks the status register’s UF bit

from generating a RFERR in the EIR.

19

OF_MSK

FIFO overflow mask. When this bit is set, the FIFO controller masks the status register’s OF bit from

generating a RFERR in the EIR.