Figure 8-14, Specify data patterns us, Command. table 8-18 describes dbmr n fields – Freescale Semiconductor MCF5480 User Manual

Page 273: Wdmreg

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

8-23

describes DBRn fields.

DBMR and DBMR1 are accessible in supervisor mode as debug control register 0x0F and 0x1F, using the

WDEBUG instruction and via the BDM port using the

WDMREG

command.

describes DBMRn fields.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

DATA (DBR/DBR1)

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

DATA (DBR/DBR1)

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

CPU + 0x0E (DBR), 0x1E (DBR1)

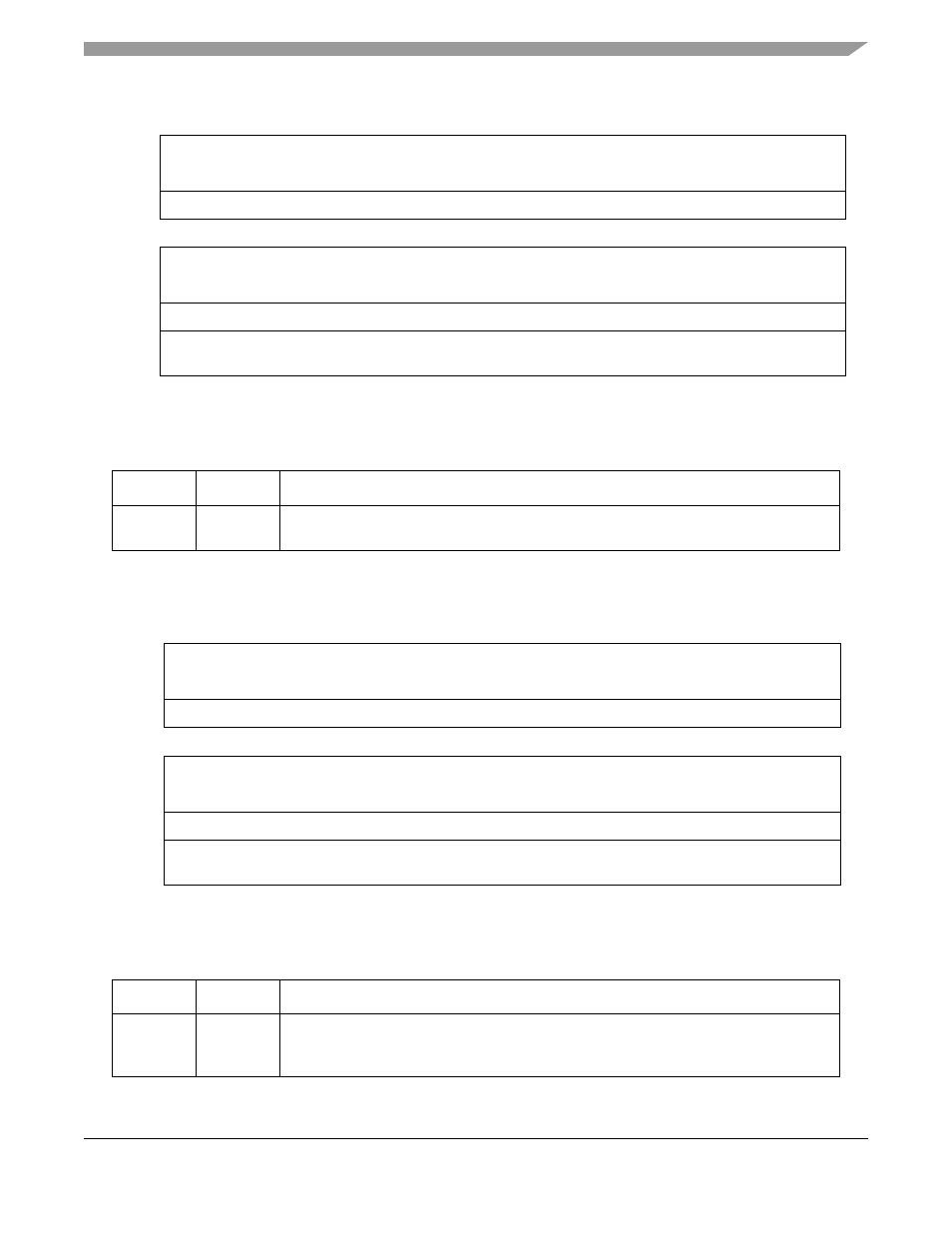

Figure 8-14. Data Breakpoint Registers (DBR/DBR1)

Table 8-17. DBRn Field Descriptions

Bits

Name

Description

31–0

DATA

Data breakpoint value. Contains the value to be compared with the data value from the

processor’s local bus as a breakpoint trigger.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

MSK (DBMR/DBMR1)

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

MSK (DBMR/DBMR1)

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

CPU + 0x0F (DBMR), 0x1F (DBMR1)

Figure 8-15. Data Breakpoint Mask Registers (DBMR/DBMR1)

Table 8-18. DBMRn Field Descriptions

Bits

Name

Description

31–0

MSK

Data breakpoint mask. The 32-bit mask for the data breakpoint trigger. Clearing a DBRn

bit allows the corresponding DBRn bit to be compared to the appropriate bit of the

processor’s local data bus. Setting a DBMRn bit causes that bit to be ignored.