Freescale Semiconductor MCF5480 User Manual

Page 502

MCF548x Reference Manual, Rev. 3

19-18

Freescale Semiconductor

19.3.2.6

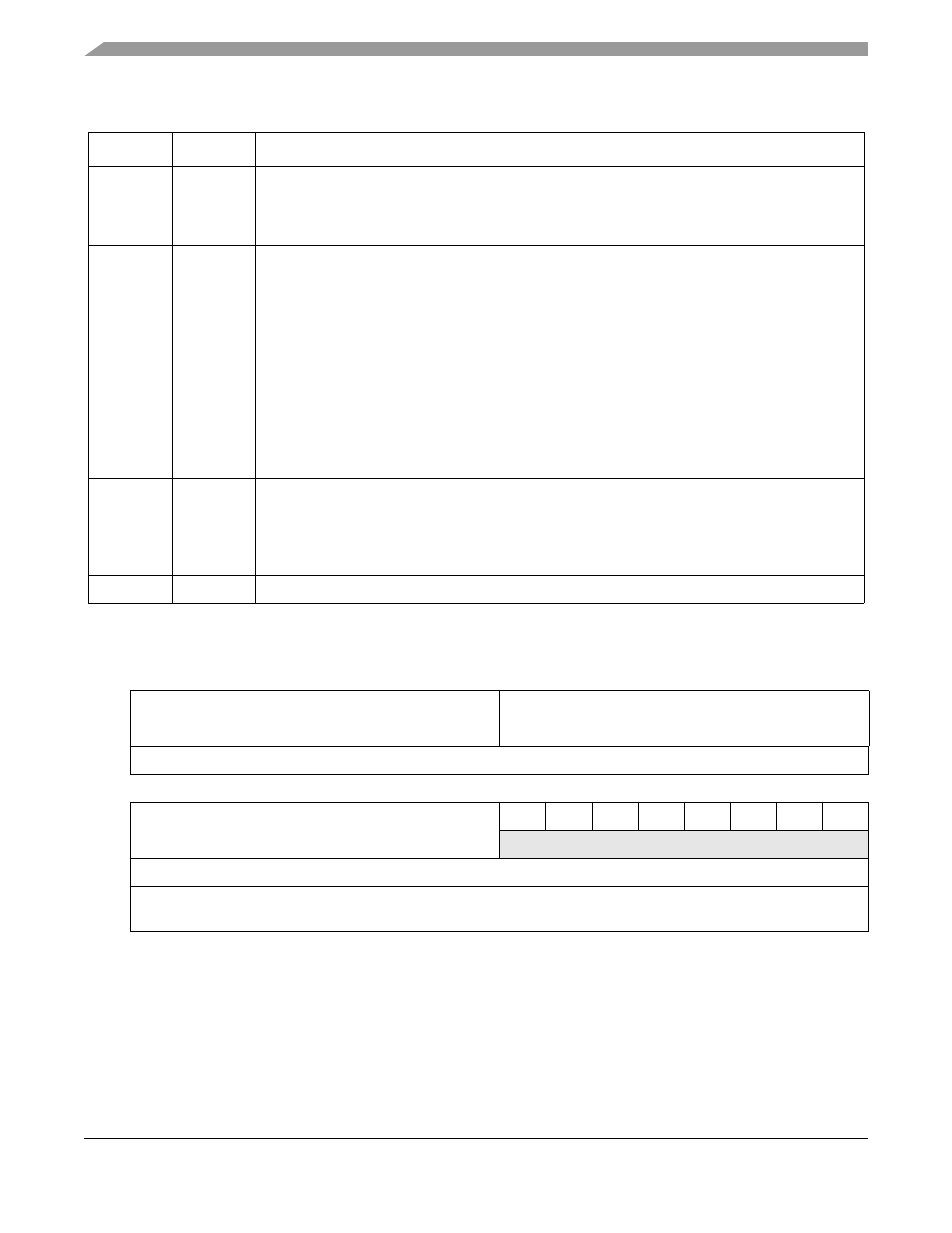

Initiator Window 1 Base/Translation Address Register (PCIIW1BTAR)

The field descriptions for this register are the same as for PCIIW0BTAR, except that they apply to Window

1.

Table 19-14. PCIIW0BTAR Field Descriptions

Bits

Name

Description

31–24

Window 0

Base

Address

One of three base address registers to determine an XL bus hit on PCI. At most, the upper byte of

the address is decoded. The Window 0 Address Mask register determines what bits of this register

to compare the XL bus address against to generate the hit.

The smallest possible Window is a 16-Mbyte block.

23–16

Window 0

Address

Mask

The Window 0 Address Mask Register masks the corresponding XL bus base address bit of the

base address for Window 0 (Window 0 Base Address) to instruct the address decode logic to

ignore or “don’t care” the bit. If the base address mask bit is set, the associated base address bit

of Window 0 is ignored when generating the PCI hit. Bit 16 masks bit 24, bit 17 masks bit 25, and

so on.

0 Corresponding address bit is used in address decode.

1 Corresponding address bit is ignored in address decode.

For XL bus accesses to Window 0 address range, this byte also determines which upper 8 bits of

the XL bus address to pass on for presentation as a PCI address. Any address bit used to decode

the XL bus address, indicated by a “0”, will be translated. This provides a way to overlay a PCI page

address onto the XL bus address. A “1” in the Address Mask byte indicates that the XL bus address

bit will be passed to PCI unaltered.

15–8

Window 0

Translation

Address

For any translated bit (described above), the corresponding value here will be driven onto the PCI

address bus for the XL bus Window 0 address hit.

The Window Translation operation can not be turned off. If a direct mapping from XL bus to PCI

space is desired, program the same value to both the Window Base Address Register and Window

Translation Address Register.

7–0

—

Reserved, should be cleared.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

Window 1 Base Address

Window 1 Address Mask

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

Window 1 Translation Address

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0xB74

Figure 19-14. Initiator Window 1 Base/Translation Address Register (PCIIW1BTAR)