13 bdm accesses of the emac registers – Freescale Semiconductor MCF5480 User Manual

Page 297

Background Debug Mode (BDM)

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

8-47

8.5.3.3.12

BDM Accesses of the Stack Pointer Registers (A7: SSP and USP)

The Version 4 ColdFire core supports two unique stack pointer (A7) registers: the supervisor stack pointer

(SSP) and the user stack pointer (USP). The hardware implementation of these two programmable-visible

32-bit registers does not uniquely identify one as the SSP and the other as the USP. Rather, the hardware

uses one 32-bit register as the currently-active A7; the other is named simply the OTHER_A7. Thus, the

contents of the two hardware registers is a function of the operating mode of the processor:

if SR[S] = 1

then

A7 = Supervisor Stack Pointer

OTHER_A7 = User Stack Pointer

else

A7 = User Stack Pointer

OTHER_A7 = Supervisor Stack Pointer

The BDM programming model supports reads and writes to A7 and OTHER_A7 directly. It is the

responsibility of the external development system to determine the mapping of A7 and OTHER_A7 to the

two program-visible definitions (supervisor and user stack pointers), based on the SR[S].

8.5.3.3.13

BDM Accesses of the EMAC Registers

The presence of rounding logic in the output datapath of the EMAC requires special care for

BDM-initiated reads and writes of its programming model. In particular, any result rounding modes must

be disabled during the read/write process so the exact bit-wise EMAC register contents are accessed.

For example, a BDM read of an accumulator (ACCx) requires the following sequence:

BdmReadACCx (

rcreg

macsr;

// read current macsr contents & save

wcreg

#0,macsr;

// disable all rounding modes

rcreg

ACCx;

// read the desired accumulator

wcreg

#saved_data,macsr;

// restore the original macsr

)

FPL6

0x81D

32 lsbs of floating-point data register 6

FPU7

0x81E

32 msbs of floating-point data register 7

FPL7

0x81F

32 lsbs of floating-point data register 7

FPIAR

0x821

Floating-point instruction address register

FPSR

0x822

Floating-point status register

FPCR

0x824

Floating-point control register

Local Memory and Module Control Registers

RAMBAR0

0xC04

RAM base address register 0

RAMBAR1

0xC05

RAM base address register 1

MBAR

0xC0F

Primary module base address register (not a core register)

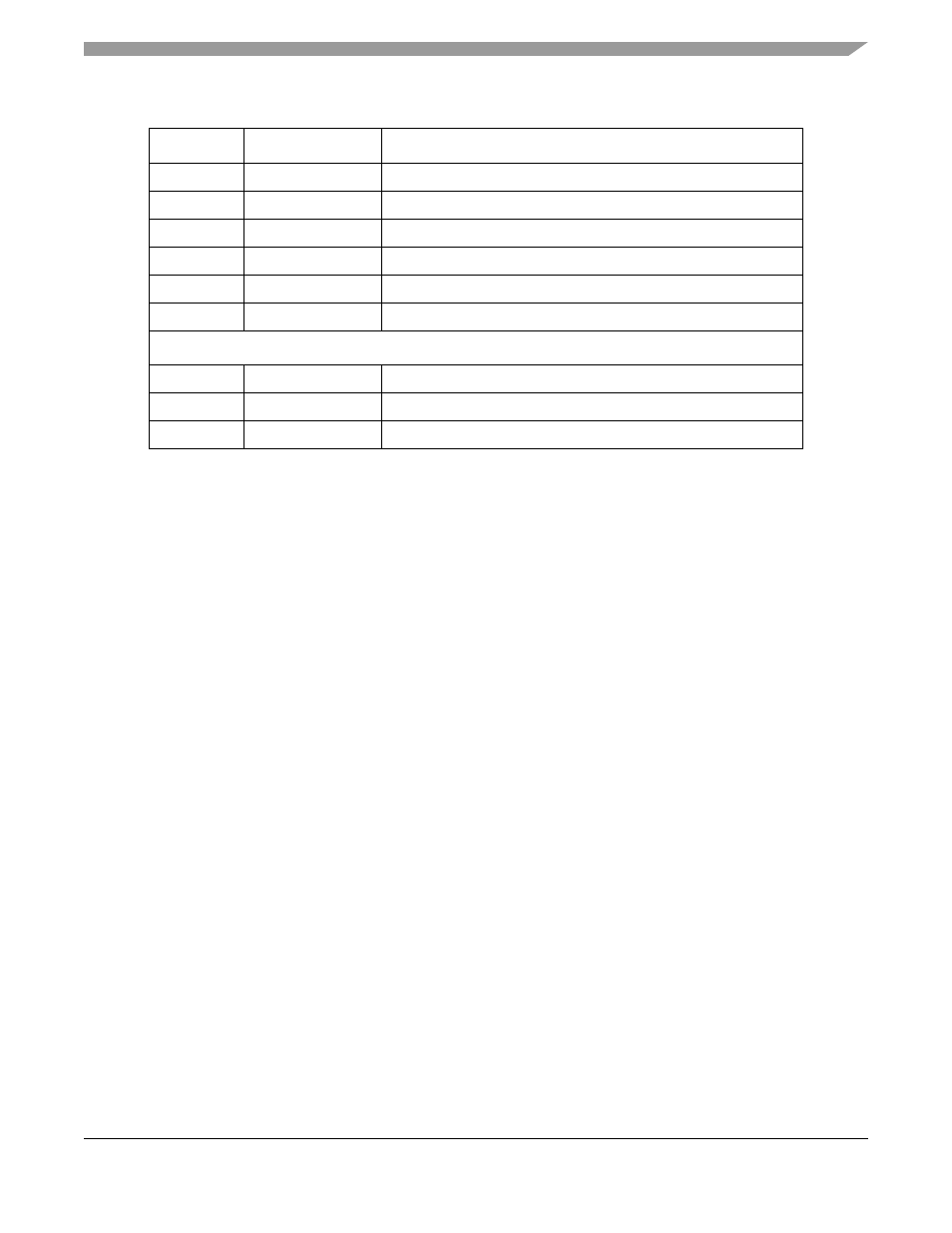

Table 8-26. ColdFire CPU Control Register Map (Continued)

Name

CPU Space (Rc)

Register Name