2 the cache at start-up, The cache at start-up -8, Figure 7-3 – Freescale Semiconductor MCF5480 User Manual

Page 228: Shows data cache or

MCF548x Reference Manual, Rev. 3

7-8

Freescale Semiconductor

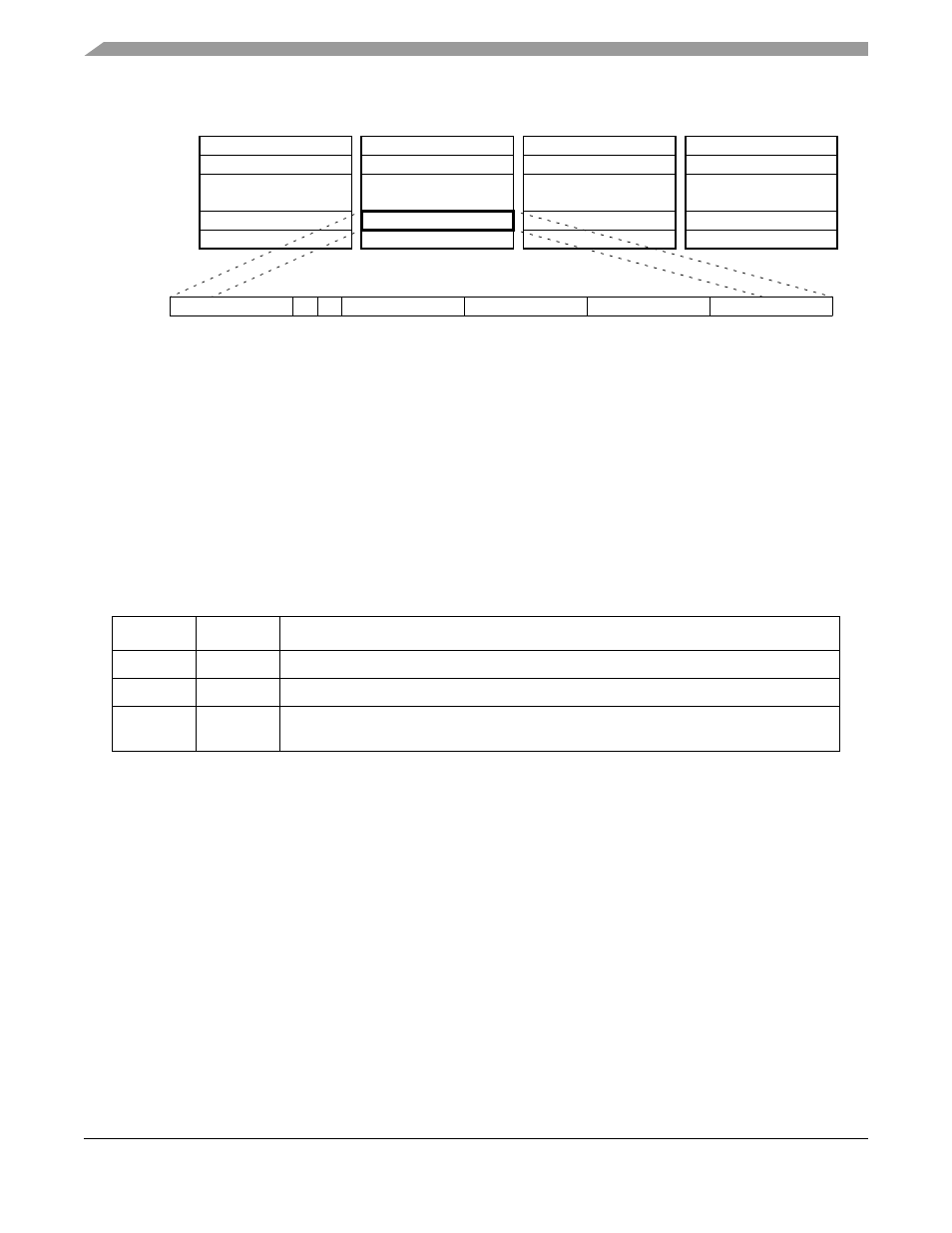

Figure 7-3. Data Cache Organization and Line Format

A set is a group of four lines (one from each level, or way), corresponding to the same index into the cache

array.

7.8.1

Cache Line States: Invalid, Valid-Unmodified, and Valid-Modified

, a data cache line can be invalid, valid-unmodified (often called exclusive), or

valid-modified. An instruction cache line can be valid or invalid.

A valid line can be explicitly invalidated by executing a CPUSHL instruction.

7.8.2

The Cache at Start-Up

(A) shows, after power-up, cache contents are undefined; V and M may be set on some lines

even though the cache may not contain the appropriate data for start up. Because reset and power-up do

not invalidate cache lines automatically, the cache should be cleared explicitly by setting

CACR[DCINVA,ICINVA] before the cache is enabled (B).

After the entire cache is flushed, cacheable entries are loaded first in way 0. If way 0 is occupied, the

cacheable entry is loaded into the same set in way 1, as shown in

(D). This process is described

in detail in

Table 7-3. Valid and Modified Bit Settings

V

M

Description

0

x

Invalid. Invalid lines are ignored during lookups.

1

0

Valid, unmodified. Cache line has valid data that matches system memory.

1

1

Valid, modified. Cache line contains most recent data, data at system memory location is

stale.

Way 0

Way 1

Way 2

Way 3

Line

Set 0

Set 1

Set 510

Set 511

•

•

•

•

•

•

•

•

•

•

•

•

TAG

V

M

Longword 0

Longword 1

Longword 2

Longword 3

Where:

TAG—21-bit address tag

V—Valid bit for line

M—Modified bit for line (data cache only)

Cache Line Format