Chapter 20 pci bus arbiter module, 1 introduction, 1 block diagram – Freescale Semiconductor MCF5480 User Manual

Page 561: 2 overview, Chapter 20, Pci bus arbiter module, Introduction -1, Block diagram -1, Overview -1, Chapter 20, “pci bus arbiter module

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

20-1

Chapter 20

PCI Bus Arbiter Module

20.1

Introduction

This chapter describes the MCF548x PCI bus arbiter module, including timing for request and grant

handshaking, the arbitration process, and the registers in the PCI bus arbiter programing model. It also

provides arbitration examples. For information on the PCI Controller, see

20.1.1

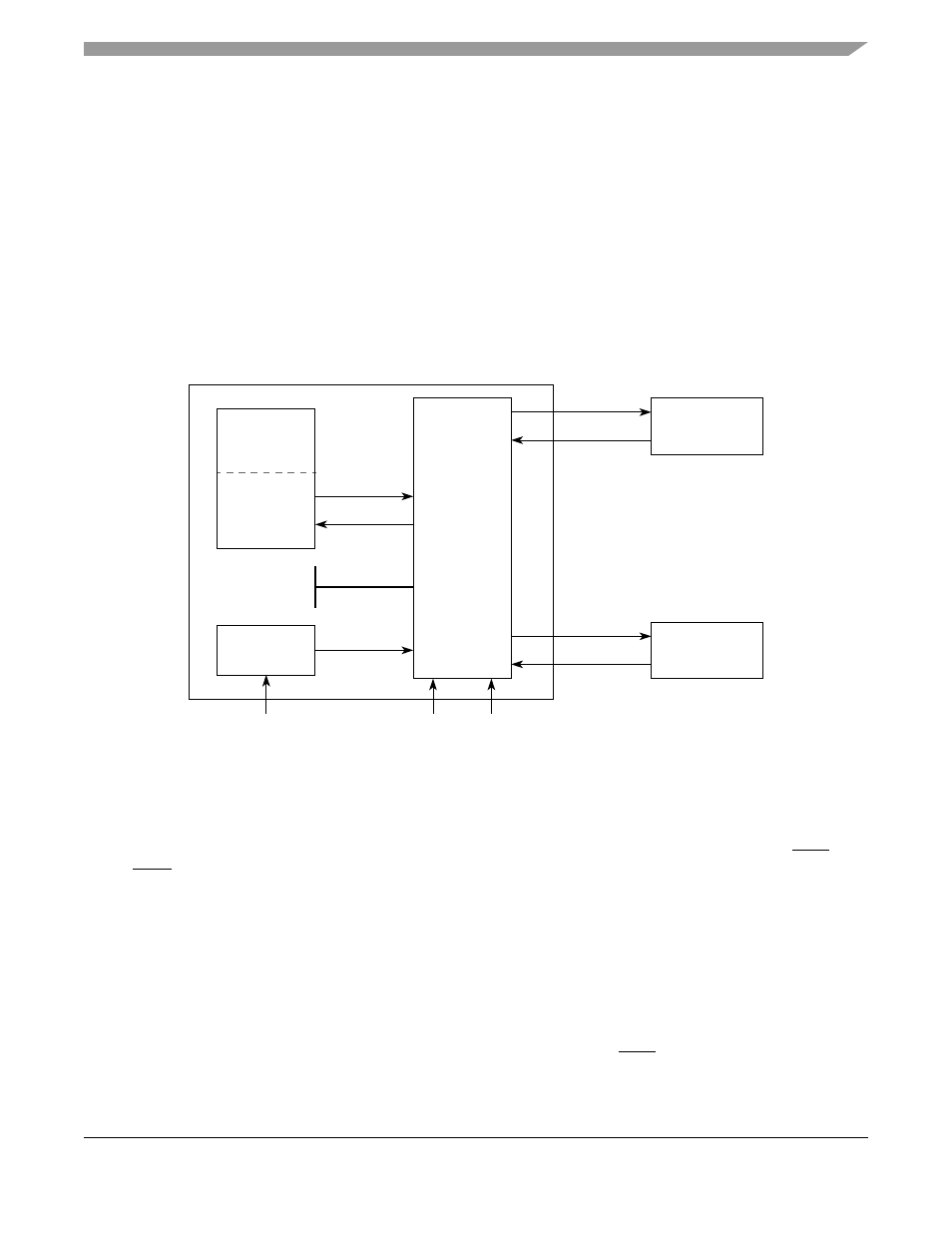

Block Diagram

Figure 20-1. PCI Arbiter Interface Diagram

20.1.2

Overview

PCI bus arbitration is access-based. Bus masters must arbitrate for each access performed on the bus. The

PCI bus uses a central arbitration scheme where each PCI master has its own unique request (REQ) and

grant (GNT) signal. A simple request-grant handshake is used to gain access to the bus.

The MCF548x contains an internal PCI bus arbiter that supports up to five external masters in addition to

the MCF548x. It can be disabled to allow for an external PCI arbiter.

The arbiter makes use of overlapped or “hidden” arbitration to reduce arbitration overhead and improve

bus utilization. Only during idle states of the PCI bus are cycles consumed due to arbitration.

When no device is using or requesting the PCI bus, the PCI arbiter parks the bus with the last master that

acquired the bus. The bus is then immediately available to the selected bus master if it should require the

use of the bus (and no other higher-priority request is pending). The selected master can immediately

initiate a transaction as long as the PCI bus is idle. It need not assert its REQ.

PCI Device 0

MCF548X PCI

Controller

Initiator

Interface

INT REQ

INT GNT

PCI Device 4

Clock Enable/

PLL

PCIBG4

PCIBR4

PCIBR0

PCIBG0

CLKIN

Slave

Bus

PCIIRDY

PCIFRM

PCI

Arbiter

CLKIN

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•