Figure 22-11 – Freescale Semiconductor MCF5480 User Manual

Page 617

Controller

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

22-15

I

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Field

CHA_1

CHA_0

AERR

—

Definition ERR

DN

ERR

DN

Reset

0x0000

R/W

W

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Field

—

Definition

Reset

0x0000

R/W

W

Reg

Addr

MBAR + 0x21008 (SIMRH), 0x 21010 (SISRH), 0x21018 (SICRH)

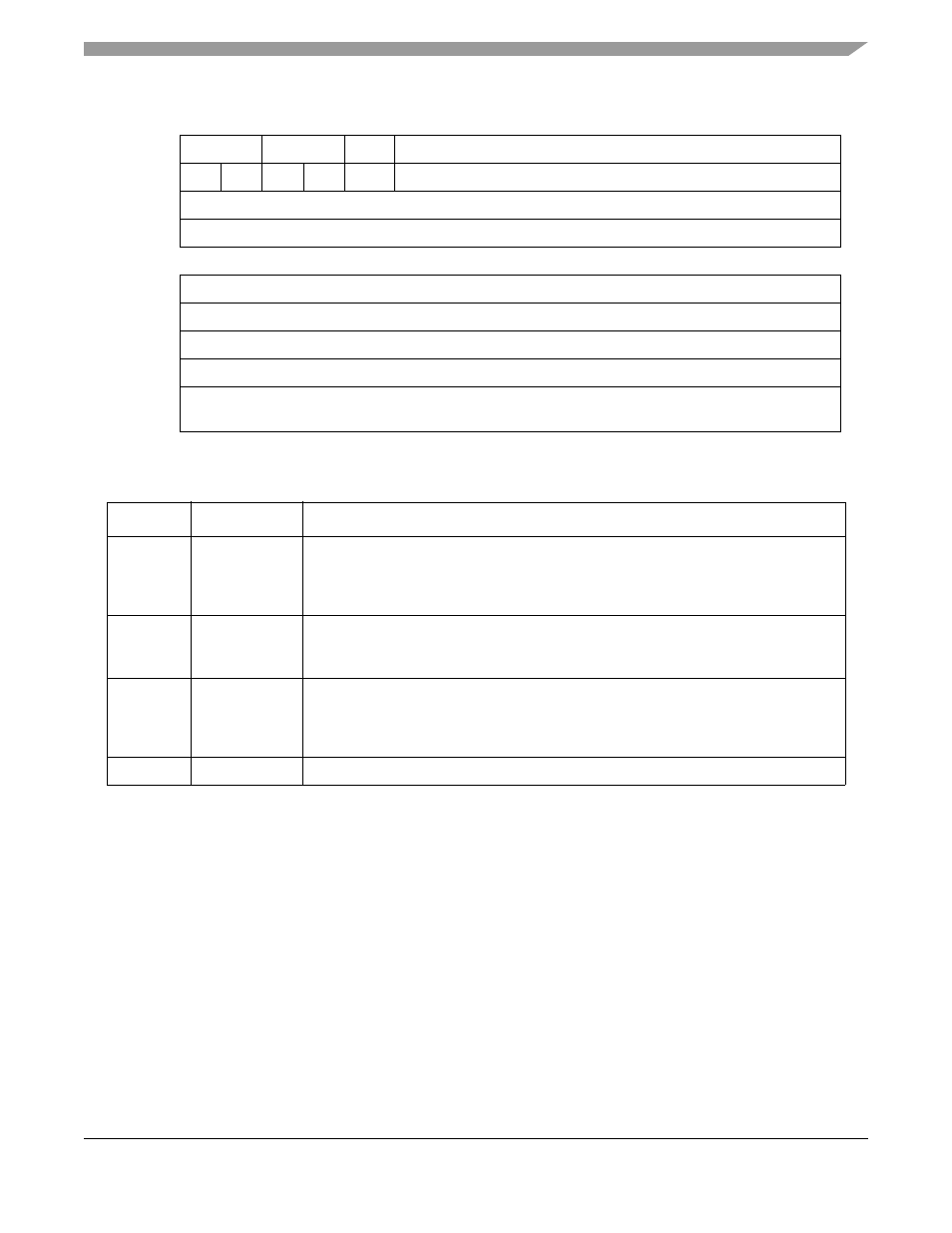

Figure 22-11. SEC Interrupt Mask, Status, and Control Registers High (SIMRH, SISRH, and SICRH)

Table 22-7. SIMRH, SISRH, and SICRH Field Descriptions

Bits

Name

Description

31, 29

CH_n_ERR_DN Channel error. Each of the channels has an error bit.

0 No error detected.

1 Error detected. Indicates that execution unit status register must be read to determine

exact cause of the error.

30, 28

CH_n_DN

Channel done. Each of the channels has a done bit.

0 Not DONE.

1 DONE bit indicates that the interrupting channel or EU has completed its operation.

27

AERR

Assignment Error bit. This bit indicates that a static assignment of a EU was attempted

on a EU which is currently in use.

0 No error detected.

1 EU Assignment Error detected.

26–0

—

Reserved, should be cleared.